System-on-a-Chip

Ein System auf einem Chip (SoC; /ˌɛsˌoʊˈsiː/ es-oh-SEE oder /sɒk/ sock), auch als System-on-a-Chip und System-on-Chip bezeichnet, ist ein integrierter Schaltkreis (auch als "Chip" bezeichnet), der alle oder die meisten Komponenten eines Computers oder eines anderen elektronischen Systems integriert. Zu diesen Komponenten gehören fast immer eine zentrale Verarbeitungseinheit (CPU), Speicherschnittstellen, On-Chip-Eingabe-/Ausgabegeräte, Eingabe-/Ausgabeschnittstellen und sekundäre Speicherschnittstellen, oft neben anderen Komponenten wie Funkmodems und einer Grafikverarbeitungseinheit (GPU) - alles auf einem einzigen Substrat oder Mikrochip. Er kann digitale, analoge, Mixed-Signal- und oft auch Hochfrequenz-Signalverarbeitungsfunktionen enthalten (andernfalls wird er nur als Anwendungsprozessor betrachtet). ⓘ

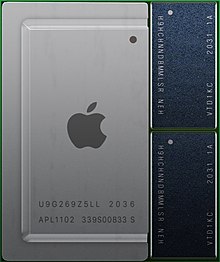

Leistungsstärkere SoCs werden oft mit dedizierten und physisch getrennten Speicher- und Sekundärspeicherchips (wie LPDDR und eUFS bzw. eMMC) gepaart, die in einer so genannten Package-on-Package-Konfiguration (PoP) über dem SoC liegen oder in der Nähe des SoC platziert werden können. Außerdem können SoCs separate drahtlose Modems verwenden. ⓘ

SoCs stehen im Gegensatz zur herkömmlichen, auf einer Hauptplatine basierenden PC-Architektur, bei der die Komponenten nach ihrer Funktion getrennt und über eine zentrale Schnittstellenplatine miteinander verbunden sind. Während eine Hauptplatine abnehmbare oder austauschbare Komponenten beherbergt und verbindet, sind bei SoCs alle diese Komponenten in einem einzigen integrierten Schaltkreis integriert. Ein SoC integriert in der Regel eine CPU, Grafik- und Speicherschnittstellen, Sekundärspeicher und USB-Konnektivität, Random-Access- und Read-Only-Speicher sowie Sekundärspeicher und/oder deren Controller auf einem einzigen Schaltungschip, während eine Hauptplatine diese Module als diskrete Komponenten oder Erweiterungskarten anschließen würde. ⓘ

Ein SoC integriert einen Mikrocontroller, Mikroprozessor oder vielleicht mehrere Prozessorkerne mit Peripheriegeräten wie einem Grafikprozessor, Wi-Fi- und Mobilfunkmodems und/oder einem oder mehreren Koprozessoren. Ähnlich wie ein Mikrocontroller einen Mikroprozessor mit Peripherieschaltungen und Speicher integriert, kann ein SoC als Integration eines Mikrocontrollers mit noch fortschrittlicheren Peripheriegeräten betrachtet werden. Einen Überblick über die Integration von Systemkomponenten finden Sie unter Systemintegration. ⓘ

Enger integrierte Computersystemdesigns verbessern die Leistung und reduzieren den Stromverbrauch sowie die Halbleiterfläche im Vergleich zu Multi-Chip-Designs mit gleicher Funktionalität. Der Preis dafür ist die geringere Austauschbarkeit der Komponenten. Definitionsgemäß sind SoC-Designs über verschiedene Komponentenmodule hinweg vollständig oder nahezu vollständig integriert. Aus diesen Gründen gibt es in der Computer-Hardware-Industrie einen allgemeinen Trend zu einer engeren Integration von Komponenten, was zum Teil auf den Einfluss von SoCs und die Lehren aus den Märkten für mobile und eingebettete Computer zurückzuführen ist. SoCs können als Teil eines größeren Trends zu eingebetteten Computern und Hardwarebeschleunigung betrachtet werden. ⓘ

SoCs sind in der mobilen Datenverarbeitung (z. B. in Smartphones und Tablet-Computern) und im Edge Computing weit verbreitet. Sie werden auch häufig in eingebetteten Systemen wie WiFi-Routern und dem Internet der Dinge eingesetzt. ⓘ

Während Systeme anfänglich aus einem Mikroprozessor- oder Mikrocontroller-IC und vielen anderen ICs für spezielle Funktionen bestanden, die auf einer Platine aufgelötet waren, lässt die heute mögliche Integrationsdichte zu, nahezu alle Funktionen auf einem einzigen IC zu vereinigen. Dabei werden digitale, analoge und Mixed-Signal-Funktionseinheiten integriert. Vorteile sind vor allem Kosteneinsparung, geringerer Energieverbrauch beziehungsweise Verlustleistung und umfassende Miniaturisierung. So ist heute beispielsweise bei Mobiltelefonen die digitale Funktion, gegebenenfalls mit Ausnahme des Speichers, auf einem IC realisiert. Auch die Schnittstellen beispielsweise zur Tastatur, zur SIM-Karte oder zum Display sind bereits auf diesem IC enthalten. ⓘ

Eine ähnliche Technik, um hohe Integrationsdichten auch von Bauelementen von stark unterschiedlicher Technik zu erreichen, ist das sogenannte System-in-Package (SiP). Dabei werden mehrere Chips in einem Gehäuse zusammengefasst. ⓘ

Arten

Im Allgemeinen lassen sich drei Arten von SoCs unterscheiden:

- SoCs, die um einen Mikrocontroller herum aufgebaut sind,

- SoCs, die um einen Mikroprozessor herum aufgebaut sind und häufig in Mobiltelefonen zu finden sind;

- Spezialisierte anwendungsspezifische integrierte Schaltkreise (SoCs), die für bestimmte Anwendungen entwickelt wurden, die nicht in die beiden oben genannten Kategorien passen. ⓘ

Anwendungen

SoCs können für jede Rechenaufgabe eingesetzt werden. Sie werden jedoch in der Regel in mobilen Computern wie Tablets, Smartphones, Smartwatches und Netbooks sowie in eingebetteten Systemen und in Anwendungen verwendet, in denen früher Mikrocontroller zum Einsatz kamen. ⓘ

Eingebettete Systeme

Wo früher nur Mikrocontroller eingesetzt werden konnten, gewinnen SoCs auf dem Markt für eingebettete Systeme zunehmend an Bedeutung. Eine engere Systemintegration bietet eine höhere Zuverlässigkeit und eine kürzere mittlere Ausfallzeit, und SoCs bieten mehr fortschrittliche Funktionen und Rechenleistung als Mikrocontroller. Zu den Anwendungen gehören KI-Beschleunigung, eingebettetes maschinelles Sehen, Datenerfassung, Telemetrie, Vektorverarbeitung und Umgebungsintelligenz. Häufig zielen eingebettete SoCs auf das Internet der Dinge, das industrielle Internet der Dinge und den Edge-Computing-Markt ab. ⓘ

Mobile Datenverarbeitung

Auf Mobile Computing basierende SoCs bündeln immer Prozessoren, Speicher, On-Chip-Caches, drahtlose Netzwerkfunktionen und oft auch Digitalkamera-Hardware und -Firmware. Mit zunehmender Größe des Arbeitsspeichers werden High-End-SoCs oft ohne Arbeitsspeicher und Flash-Speicher auskommen und stattdessen werden der Arbeitsspeicher und der Flash-Speicher direkt neben oder über dem SoC platziert (Package on Package). Einige Beispiele für SoCs für die mobile Datenverarbeitung sind:

- Samsung Electronics: Liste, typischerweise basierend auf ARM

- Exynos, hauptsächlich in Samsungs Galaxy-Smartphones verwendet

- Qualcomm:

Personal Computer

1992 stellte Acorn Computers die Personalcomputer A3010, A3020 und A4000 mit dem ARM250 SoC her. Dieser kombinierte den ursprünglichen Acorn ARM2-Prozessor mit einem Speicher-Controller (MEMC), einem Video-Controller (VIDC) und einem I/O-Controller (IOC). In früheren Acorn ARM-betriebenen Computern waren dies vier diskrete Chips. Der ARM7500-Chip war ein SoC der zweiten Generation, der auf dem ARM700, dem VIDC20 und dem IOMD-Controller basierte und in eingebetteten Geräten wie Set-Top-Boxen sowie in späteren Acorn-Personalcomputern weit verbreitet war. ⓘ

Ab 2018 werden SoCs in Mainstream-Personalcomputern eingesetzt. Sie werden insbesondere in Laptops und Tablet-PCs eingesetzt. Die Hersteller von Tablets und Laptops haben von den Märkten für eingebettete Systeme und Smartphones gelernt, was die Senkung des Stromverbrauchs, die Verbesserung der Leistung und Zuverlässigkeit durch eine engere Integration von Hardware- und Firmware-Modulen sowie die Integration von LTE und anderen drahtlosen Netzwerkkommunikationen auf dem Chip (integrierte Netzwerkschnittstellen-Controller) betrifft. ⓘ

ARM-basiert:

- Qualcomm Snapdragon

- ARM250

- ARM7500(FE)

- Apple M1 ⓘ

x86-basiert:

- Intel Core CULV ⓘ

Aufbau

Ein SoC besteht aus Hardware-Funktionseinheiten, einschließlich Mikroprozessoren, auf denen Softwarecode ausgeführt wird, sowie aus einem Kommunikationssubsystem, das diese Funktionsmodule miteinander verbindet, steuert, leitet und eine Schnittstelle zwischen ihnen bildet. ⓘ

Funktionelle Komponenten

Prozessorkerne

Ein SoC muss mindestens einen Prozessorkern haben, aber in der Regel hat ein SoC mehr als einen Kern. Prozessorkerne können ein Mikrocontroller, ein Mikroprozessor (μP), ein digitaler Signalprozessor (DSP) oder ein anwendungsspezifischer Befehlssatzprozessor (ASIP) sein. ASIPs verfügen über Befehlssätze, die auf einen Anwendungsbereich zugeschnitten und so konzipiert sind, dass sie für eine bestimmte Art von Arbeitslast effizienter sind als allgemeine Befehle. Multiprozessor-SoCs haben per Definition mehr als einen Prozessorkern. ⓘ

Unabhängig davon, ob es sich um Single-Core-, Multi-Core- oder Many-Core-Prozessoren handelt, verwenden SoC-Prozessorkerne in der Regel RISC-Befehlssatzarchitekturen. RISC-Architekturen sind für SoCs gegenüber CISC-Prozessoren vorteilhaft, da sie weniger digitale Logik und damit weniger Strom und Fläche auf der Platine benötigen, und auf dem Markt für eingebettete und mobile Computer sind Fläche und Stromverbrauch oft stark eingeschränkt. Insbesondere SoC-Prozessorkerne verwenden häufig die ARM-Architektur, da es sich um einen Soft-Prozessor handelt, der als IP-Kern spezifiziert ist und mehr Strom spart als x86. ⓘ

Speicher

SoCs müssen über Halbleiterspeicherblöcke verfügen, um ihre Berechnungen durchführen zu können, ebenso wie Mikrocontroller und andere eingebettete Systeme. Je nach Anwendung kann der SoC-Speicher eine Speicherhierarchie und eine Cache-Hierarchie bilden. Auf dem Markt für mobile Computer ist dies üblich, aber bei vielen eingebetteten Mikrocontrollern mit geringem Stromverbrauch ist dies nicht erforderlich. Zu den Speichertechnologien für SoCs gehören Festwertspeicher (ROM), Direktzugriffsspeicher (RAM), elektrisch löschbarer programmierbarer ROM (EEPROM) und Flash-Speicher. Wie in anderen Computersystemen kann RAM in relativ schnelles, aber teureres statisches RAM (SRAM) und das langsamere, aber billigere dynamische RAM (DRAM) unterteilt werden. Wenn ein SoC über eine Cache-Hierarchie verfügt, wird SRAM in der Regel für die Implementierung von Prozessorregistern und den integrierten Caches der Kerne verwendet, während DRAM als Hauptspeicher eingesetzt wird. "Hauptspeicher" kann spezifisch für einen einzelnen Prozessor sein (der aus mehreren Kernen bestehen kann), wenn der SoC über mehrere Prozessoren verfügt. In diesem Fall handelt es sich um einen verteilten Speicher, der über § Intermodul-Kommunikation auf dem Chip übertragen werden muss, damit ein anderer Prozessor darauf zugreifen kann. Weitere Informationen zu Speicherproblemen bei Multiprozessoren finden Sie unter Cache-Kohärenz und Speicherlatenz. ⓘ

Schnittstellen

SoCs verfügen über externe Schnittstellen, in der Regel für Kommunikationsprotokolle. Diese beruhen häufig auf Industriestandards wie USB, FireWire, Ethernet, USART, SPI, HDMI, I²C usw. Diese Schnittstellen unterscheiden sich je nach der vorgesehenen Anwendung. Drahtlose Netzwerkprotokolle wie Wi-Fi, Bluetooth, 6LoWPAN und Nahfeldkommunikation können ebenfalls unterstützt werden. ⓘ

Bei Bedarf enthalten SoCs analoge Schnittstellen, einschließlich Analog-Digital- und Digital-Analog-Wandlern, häufig für die Signalverarbeitung. Diese können mit verschiedenen Arten von Sensoren oder Aktuatoren, einschließlich intelligenter Messwandler, verbunden werden. Sie können mit anwendungsspezifischen Modulen oder Abschirmungen verbunden sein. Sie können aber auch intern in den SoC integriert sein, z. B. wenn ein analoger Sensor in den SoC eingebaut ist und seine Messwerte für die mathematische Verarbeitung in digitale Signale umgewandelt werden müssen. ⓘ

Digitale Signalprozessoren

Um den eigentlichen Hauptprozessor des SoCs zu entlasten, sind je nach Anwendung auch spezialisierte Prozessoren enthalten. Dies können beispielsweise Prozessoren zur digitalen Signalverarbeitung sein (DSPs) oder beispielsweise Ver-/Entschlüsselungseinheiten oder sonstige Hardwarebeschleuniger wie Physikbeschleuniger. Hierzu können einzelne Berechnungen oder auch nur Teile davon ausgelagert werden. Diese werden entweder ganz vom Coprozessor übernommen, oder der Hauptprozessor reicht nur einzelne, besonders rechenintensive Befehle weiter. Diese werden dann unter Umständen nicht mehr als Software auf einer General Purpose CPU oder DSP ausgeführt, sondern direkt in Hardware implementiert. Dies ist zumindest in FPGAs und ASICs gängige Praxis und wird daher auch dementsprechend direkt von den EDA-Werkzeugen unterstützt. Viele moderne FPGAs wie Virtex4/5 oder StratixII/III enthalten auch sogenannte DSP-Makros, womit sehr schnell in vielen parallelen Pfaden sogenannte MAC-Befehle ausgeführt werden können. ⓘ

Digitale Signalprozessorkerne (DSP) sind häufig in SoCs enthalten. Sie führen Signalverarbeitungsoperationen in SoCs für Sensoren, Aktoren, Datenerfassung, Datenanalyse und Multimediaverarbeitung durch. DSP-Cores verfügen in der Regel über VLIW- (Very Long Instruction Word) und SIMD-Befehlssatzarchitekturen (Single Instruction, Multiple Data) und eignen sich daher sehr gut für die Nutzung von Parallelität auf Befehlsebene durch Parallelverarbeitung und superskalare Ausführung. DSP-Cores enthalten meist anwendungsspezifische Befehle und sind daher in der Regel anwendungsspezifische Befehlssatzprozessoren (ASIP). Solche anwendungsspezifischen Befehle entsprechen speziellen Hardware-Funktionseinheiten, die diese Befehle berechnen. ⓘ

Typische DSP-Befehle sind Multiplikation-Akkumulation, Fast-Fourier-Transformation, fusionierte Multiplikation-Addition und Faltung. ⓘ

Andere

Wie andere Computersysteme benötigen SoCs Zeitquellen zur Erzeugung von Taktsignalen, zur Steuerung der Ausführung von SoC-Funktionen und zur Bereitstellung von Zeitkontext für die Signalverarbeitungsanwendungen des SoCs, falls erforderlich. Beliebte Zeitquellen sind Quarzoszillatoren und Phasenregelkreise. ⓘ

SoC-Peripheriegeräte wie Zähler-Timer, Echtzeit-Timer und Power-on-Reset-Generatoren. SoCs enthalten auch Spannungsregler und Stromverwaltungsschaltungen. ⓘ

Modulübergreifende Kommunikation

SoCs bestehen aus vielen Ausführungseinheiten. Diese Einheiten müssen häufig Daten und Anweisungen hin- und herschicken. Aus diesem Grund benötigen alle SoCs außer den trivialsten Kommunikations-Subsystemen. Ursprünglich wurden, wie bei anderen Mikrocomputertechnologien auch, Datenbusarchitekturen verwendet, aber in letzter Zeit haben Designs, die auf spärlichen Interkommunikationsnetzwerken basieren, die als Networks-on-Chip (NoC) bekannt sind, an Bedeutung gewonnen, und es wird prognostiziert, dass sie in naher Zukunft die Busarchitekturen für SoC-Designs ablösen werden. ⓘ

Busbasierte Kommunikation

In der Vergangenheit verband ein gemeinsamer globaler Computerbus in der Regel die verschiedenen Komponenten, auch "Blöcke" genannt, eines SoCs. Ein sehr gebräuchlicher Bus für die SoC-Kommunikation ist der lizenzfreie Standard Advanced Microcontroller Bus Architecture (AMBA) von ARM. ⓘ

Direktspeicherzugriffs-Controller leiten Daten direkt zwischen externen Schnittstellen und dem SoC-Speicher weiter, wobei die CPU oder die Steuereinheit umgangen werden, wodurch der Datendurchsatz des SoC erhöht wird. Dies ist vergleichbar mit einigen Gerätetreibern von Peripheriegeräten auf komponentenbasierten Multi-Chip-Modul-PC-Architekturen. ⓘ

Computerbusse sind in ihrer Skalierbarkeit begrenzt, da sie nur bis zu zehn Kerne (Multicore) auf einem einzigen Chip unterstützen. Die Verzögerung der Leitungen ist aufgrund der fortlaufenden Miniaturisierung nicht skalierbar, die Systemleistung skaliert nicht mit der Anzahl der angeschlossenen Kerne, die Betriebsfrequenz des SoC muss mit jedem zusätzlich angeschlossenen Kern sinken, damit der Stromverbrauch aufrechterhalten werden kann, und lange Leitungen verbrauchen große Mengen an elektrischer Energie. Diese Herausforderungen sind für die Unterstützung von Systemen mit vielen Kernen auf einem Chip unerschwinglich. ⓘ

Netzwerk auf einem Chip

In den späten 2010er Jahren hat sich ein Trend zu SoCs entwickelt, die Kommunikations-Subsysteme in Form einer netzwerkähnlichen Topologie anstelle von busbasierten Protokollen implementieren. Der Trend zu mehr Prozessorkernen auf SoCs hat dazu geführt, dass die Kommunikationseffizienz auf dem Chip zu einem der wichtigsten Faktoren bei der Bestimmung der Gesamtsystemleistung und -kosten geworden ist. Dies hat zur Entstehung von Verbindungsnetzwerken mit Router-basierter Paketvermittlung geführt, die als "Networks on Chip" (NoCs) bekannt sind, um die Engpässe von busbasierten Netzwerken zu überwinden. ⓘ

Netzwerke auf dem Chip haben Vorteile wie ziel- und anwendungsspezifisches Routing, höhere Energieeffizienz und geringere Möglichkeit von Buskonflikten. Network-on-Chip-Architekturen orientieren sich an Kommunikationsprotokollen wie TCP und der Internet-Protokollsuite für die On-Chip-Kommunikation, obwohl sie in der Regel weniger Netzwerkschichten aufweisen. Optimale Network-on-Chip-Netzwerkarchitekturen sind ein aktuelles Thema von großem Forschungsinteresse. NoC-Architekturen reichen von traditionellen Netzwerktopologien für verteilte Datenverarbeitung wie Torus-, Hyperwürfel-, Maschen- und Baumnetze über genetische Algorithmen für die Zeitplanung bis hin zu randomisierten Algorithmen wie Random Walks mit Verzweigung und randomisierter Time to Live (TTL). ⓘ

Viele SoC-Forscher betrachten NoC-Architekturen als die Zukunft des SoC-Designs, da sie nachweislich die Anforderungen an Leistung und Durchsatz von SoC-Designs effizient erfüllen können. Die derzeitigen NoC-Architekturen sind zweidimensional. Das 2D-IC-Design bietet nur begrenzte Möglichkeiten für die Grundrissplanung, da die Anzahl der Kerne in SoCs zunimmt. Mit dem Aufkommen dreidimensionaler integrierter Schaltungen (3DICs) streben SoC-Designer daher den Aufbau dreidimensionaler On-Chip-Netzwerke an, die als 3DNoCs bekannt sind. ⓘ

Entwurfsablauf

Ein System auf einem Chip besteht sowohl aus der in § Struktur beschriebenen Hardware als auch aus der Software, die die Mikrocontroller-, Mikroprozessor- oder digitalen Signalprozessor-Kerne, Peripheriegeräte und Schnittstellen steuert. Der Entwurfsablauf für ein SoC zielt darauf ab, diese Hardware und Software gleichzeitig zu entwickeln, was auch als architektonischer Co-Entwurf bezeichnet wird. Der Entwurfsablauf muss auch Optimierungen (§ Optimierungsziele) und Beschränkungen berücksichtigen. ⓘ

Die meisten SoCs werden auf der Grundlage von vorqualifizierten IP-Kernspezifikationen für die oben beschriebenen Hardwareelemente und Ausführungseinheiten (zusammenfassend "Blöcke" genannt) entwickelt, zusammen mit Software-Gerätetreibern, die deren Betrieb steuern können. Von besonderer Bedeutung sind die Protokollstapel, die Industriestandard-Schnittstellen wie USB steuern. Die Hardware-Blöcke werden mit computergestützten Entwurfswerkzeugen zusammengestellt, insbesondere mit Werkzeugen zur Automatisierung des Elektronikentwurfs; die Software-Module werden mit einer integrierten Software-Entwicklungsumgebung integriert. ⓘ

SoC-Komponenten werden häufig auch in höheren Programmiersprachen wie C++, MATLAB oder SystemC entworfen und mit High-Level-Synthese-Werkzeugen (HLS) wie C zu HDL oder Flow zu HDL in RTL-Designs umgewandelt. HLS-Produkte, die so genannte "algorithmische Synthese", ermöglichen es Entwicklern, mit C++ System-, Schaltungs-, Software- und Verifikationsebenen zu modellieren und zu synthetisieren, und zwar in einer Hochsprache, die Computeringenieuren allgemein bekannt ist, und zwar unabhängig von den Zeitskalen, die normalerweise in HDL spezifiziert werden. Andere Komponenten können Software bleiben und auf Soft-Core-Prozessoren kompiliert und eingebettet werden, die im SoC als Module in HDL als IP-Cores enthalten sind. ⓘ

Sobald die Architektur des SoC definiert ist, werden alle neuen Hardwareelemente in einer abstrakten Hardwarebeschreibungssprache, der so genannten Registertransferebene (RTL), geschrieben, die das Schaltungsverhalten definiert, oder durch High-Level-Synthese aus einer Hochsprache in RTL synthetisiert. Diese Elemente werden in einer Hardwarebeschreibungssprache miteinander verbunden, um das vollständige SoC-Design zu erstellen. Die Logik, die zur Verbindung dieser Komponenten und zur Konvertierung zwischen möglicherweise unterschiedlichen Schnittstellen verschiedener Anbieter spezifiziert ist, wird als Glue-Logik bezeichnet. ⓘ

SoCs werden heute zumeist nicht völlig neu entwickelt, sondern die Entwürfe basieren – zumindest in Teilen – auf vorhandenen oder erworbenen Komponenten, sogenannten IP-Kernen. Dies sind beispielsweise Makros für vollständige CPU-Kerne, oder Koprozessoren – etwa als Hardwarebeschleuniger für Verschlüsselungs- oder Grafikberechnungen. Ebenso sind dies Peripherieblöcke zur Implementierung von Speicher-, Ethernet-, Bluetooth- oder sonstigen Schnittstellen, oder auch komplette Speichereinheiten inklusive deren Verwaltung. ⓘ

Viele Standardkomponenten sind bei EDA-Werkzeugen der Chip-Hersteller in proprietärer Form kostenlos enthalten. Andere Komponenten können vom Chip-Hersteller oder anderen IP-Lieferanten wie z. B. ARM, Transmeta oder kleineren oft sehr spezialisierten Entwicklungsunternehmen lizenziert werden. Oftmals lassen sich solche IP-Kerne über Parameter dem Verwendungszweck angepasst generieren, beispielsweise in Form der Pipelinelänge, der Cachegröße oder den Busbitbreiten. ⓘ

Weitere benötigte Komponenten eines SoC wurden beispielsweise bereits in früheren Projekten entwickelt und können im Idealfall direkt eingesetzt werden – oder es müssen Änderungen vorgenommen werden, bestenfalls genügt eine Parametrisierung der IP-Kerne. Eine weitere Möglichkeit ist das Verwenden „freier Hardware“. So entstehen auch im Hardwarebereich immer mehr Open-Source-Projekte (z. B. auf OpenCores.org), die sich oft noch im Entwicklungsstadium befinden. Was hier gegebenenfalls fehlt, muss der Nutzer selbst entwickeln oder entwickeln lassen. ⓘ

Die Übergänge, was in Software und was in Hardware umgesetzt wird, sind anwendungsabhängig zunehmend fließend – siehe Software Defined Radio (SDR). ⓘ

Entwurfsverifizierung

Die Chips werden auf ihre Korrektheit überprüft, bevor sie an eine Halbleiter-Gießerei geschickt werden. Dieser Prozess wird als Funktionsprüfung bezeichnet und macht einen erheblichen Teil des Zeit- und Energieaufwands im Lebenszyklus des Chipdesigns aus, der oft mit 70 % angegeben wird. Mit der zunehmenden Komplexität der Chips werden Hardware-Verifikationssprachen wie SystemVerilog, SystemC, e und OpenVera verwendet. In der Verifikationsphase gefundene Fehler werden dem Entwickler gemeldet. ⓘ

Traditionell haben Ingenieure Simulationsbeschleunigung, Emulation oder Prototyping auf reprogrammierbarer Hardware eingesetzt, um Hardware und Software für SoC-Designs vor der Fertigstellung des Designs, dem sogenannten Tape-out, zu verifizieren und zu debuggen. Feldprogrammierbare Gate-Arrays (FPGAs) werden für das Prototyping von SoCs bevorzugt, da FPGA-Prototypen reprogrammierbar sind, Debugging ermöglichen und flexibler sind als anwendungsspezifische integrierte Schaltungen (ASICs). ⓘ

Mit ihrer hohen Kapazität und schnellen Kompilierungszeit sind Simulationsbeschleunigung und Emulation leistungsstarke Technologien, die einen umfassenden Einblick in Systeme ermöglichen. Beide Technologien arbeiten jedoch langsam, in der Größenordnung von MHz, was deutlich langsamer sein kann - bis zu 100 Mal langsamer - als die Betriebsfrequenz des SoC. Beschleunigungs- und Emulationsboxen sind außerdem sehr groß und mit über 1 Million US-Dollar teuer. ⓘ

Bei FPGA-Prototypen hingegen werden FPGAs direkt eingesetzt, damit die Ingenieure das System bei oder nahe der vollen Betriebsfrequenz mit realen Stimuli validieren und testen können. Tools wie Certus werden verwendet, um Sonden in die FPGA-RTL einzufügen, die Signale zur Beobachtung verfügbar machen. Dies wird zum Debuggen von Hardware-, Firmware- und Software-Interaktionen über mehrere FPGAs hinweg mit ähnlichen Funktionen wie bei einem Logikanalysator verwendet. ⓘ

Parallel dazu werden die Hardwareelemente gruppiert und durchlaufen einen Prozess der Logiksynthese, bei dem Leistungseinschränkungen wie Betriebsfrequenz und erwartete Signalverzögerungen angewendet werden. Das Ergebnis ist eine so genannte Netzliste, die den Entwurf als physische Schaltung und seine Verbindungen beschreibt. Diese Netzlisten werden mit der Klebelogik kombiniert, die die Komponenten verbindet, um die schematische Beschreibung des SoC als Schaltkreis zu erstellen, der auf einen Chip gedruckt werden kann. Dieser Prozess wird als Place and Route bezeichnet und geht dem Tape-out voraus, falls die SoCs als anwendungsspezifische integrierte Schaltkreise (ASIC) hergestellt werden. ⓘ

Ziele der Optimierung

SoCs müssen den Energieverbrauch, die Fläche auf dem Chip, die Kommunikation, die Positionierung für die Lokalisierung zwischen modularen Einheiten und andere Faktoren optimieren. Die Optimierung ist notwendigerweise ein Designziel von SoCs. Wäre eine Optimierung nicht notwendig, würden die Ingenieure eine Multi-Chip-Modul-Architektur verwenden, ohne die Flächennutzung, den Stromverbrauch oder die Leistung des Systems in gleichem Maße zu berücksichtigen. ⓘ

Es folgen allgemeine Optimierungsziele für SoC-Entwürfe mit entsprechenden Erklärungen. Im Allgemeinen kann die Optimierung jeder dieser Größen ein schweres kombinatorisches Optimierungsproblem darstellen, das sogar ziemlich leicht NP-schwer werden kann. Daher sind oft hochentwickelte Optimierungsalgorithmen erforderlich, und in einigen Fällen kann es sinnvoll sein, Näherungsalgorithmen oder Heuristiken zu verwenden. Darüber hinaus enthalten die meisten SoC-Designs mehrere Variablen, die gleichzeitig optimiert werden müssen, so dass beim SoC-Design nach Pareto-effizienten Lösungen gesucht wird. Oftmals stehen die Ziele der Optimierung einiger dieser Größen in direktem Widerspruch zueinander, was die Komplexität der Designoptimierung von SoCs weiter erhöht und Kompromisse beim Systemdesign einführt. ⓘ

Weitere Informationen zu Kompromissen und zur Anforderungsanalyse finden Sie unter Requirements Engineering. ⓘ

Zielvorgaben

Leistungsaufnahme

SoCs werden so optimiert, dass sie möglichst wenig Strom verbrauchen, um die Funktionen des SoCs auszuführen. Die meisten SoCs müssen wenig Strom verbrauchen. SoC-Systeme benötigen oft eine lange Batterielebensdauer (z. B. Smartphones), können möglicherweise Monate oder Jahre ohne Stromquelle auskommen und müssen dennoch autonom funktionieren, und oft wird der Stromverbrauch durch eine große Anzahl eingebetteter SoCs begrenzt, die in einem Gebiet miteinander vernetzt sind. Darüber hinaus können die Energiekosten hoch sein, und die Einsparung von Energie verringert die Gesamtbetriebskosten des SoC. Schließlich kann die durch den hohen Energieverbrauch entstehende Abwärme andere Schaltungskomponenten beschädigen, wenn zu viel Wärme abgeleitet wird, was ein weiterer pragmatischer Grund für die Energieeinsparung ist. Die in einem Schaltkreis verbrauchte Energiemenge ist das Integral der verbrauchten Leistung in Bezug auf die Zeit, und die durchschnittliche Rate des Energieverbrauchs ist das Produkt aus Strom und Spannung. Nach dem Ohm'schen Gesetz ist die Leistung gleich dem Quadrat des Stroms mal dem Widerstand oder dem Quadrat der Spannung geteilt durch den Widerstand:

Leistung pro Watt

SoCs werden optimiert, um die Energieeffizienz in Bezug auf die Leistung pro Watt zu maximieren: Maximieren Sie die Leistung des SoCs bei einem bestimmten Stromverbrauchsbudget. Viele Anwendungen wie Edge Computing, verteilte Verarbeitung und Ambient Intelligence erfordern ein bestimmtes Maß an Rechenleistung, aber die Leistung ist in den meisten SoC-Umgebungen begrenzt. Die ARM-Architektur bietet in eingebetteten Systemen eine höhere Leistung pro Watt als x86, weshalb sie für die meisten SoC-Anwendungen, die einen eingebetteten Prozessor erfordern, gegenüber x86 bevorzugt wird. ⓘ

Abwärme

SoC-Designs werden optimiert, um die Abwärme auf dem Chip zu minimieren. Wie bei anderen integrierten Schaltkreisen ist die durch die hohe Leistungsdichte erzeugte Wärme der Engpass für eine weitere Miniaturisierung der Komponenten. Die Leistungsdichten von integrierten Hochgeschwindigkeitsschaltungen, insbesondere von Mikroprozessoren und SoCs, sind sehr ungleichmäßig geworden. Zu viel Abwärme kann die Schaltungen beschädigen und die Zuverlässigkeit der Schaltung mit der Zeit beeinträchtigen. Hohe Temperaturen und thermischer Stress wirken sich negativ auf die Zuverlässigkeit, Stressmigration, die Verkürzung der mittleren Zeit zwischen zwei Ausfällen, Elektromigration, Drahtbonding, Metastabilität und andere Leistungseinbußen der SoC aus. ⓘ

Insbesondere befinden sich die meisten SoCs auf einer kleinen Fläche oder in einem kleinen Volumen, so dass sich die Auswirkungen der Abwärme noch verstärken, da es nur wenig Platz gibt, um sie aus dem System herauszuleiten. Aufgrund der hohen Anzahl von Transistoren auf modernen Bauelementen ist ein Layout mit ausreichendem Durchsatz und hoher Transistordichte oft physikalisch realisierbar, würde aber zu inakzeptabel hohen Wärmemengen im Volumen der Schaltung führen. ⓘ

Diese thermischen Effekte zwingen SoC- und andere Chipdesigner dazu, konservative Designmargen anzuwenden und weniger leistungsfähige Geräte zu entwickeln, um das Risiko eines katastrophalen Ausfalls zu mindern. Aufgrund der höheren Transistordichte bei kleiner werdenden Längenskalen erzeugt jede Prozessgeneration mehr Wärme als die vorherige. Erschwerend kommt hinzu, dass SoC-Architekturen in der Regel heterogen sind, was zu räumlich inhomogenen Wärmeströmen führt, die durch eine einheitliche passive Kühlung nicht wirksam gemildert werden können. ⓘ

Durchsatz

SoCs werden optimiert, um den Rechen- und Kommunikationsdurchsatz zu maximieren. ⓘ

Latenz

SoCs werden so optimiert, dass die Latenzzeit für einige oder alle ihrer Funktionen minimiert wird. Dies kann erreicht werden, indem die Elemente in angemessener Nähe zueinander angeordnet werden, um die Verbindungsverzögerungen zu minimieren und die Geschwindigkeit zu maximieren, mit der Daten zwischen Modulen, Funktionseinheiten und Speichern übertragen werden. Im Allgemeinen ist die Optimierung zur Minimierung der Latenzzeit ein NP-komplettes Problem, das dem Problem der booleschen Erfüllbarkeit entspricht. ⓘ

Bei Tasks, die auf Prozessorkernen laufen, können Latenz und Durchsatz durch Task-Scheduling verbessert werden. Einige Tasks laufen jedoch in anwendungsspezifischen Hardware-Einheiten, und selbst Task-Scheduling reicht möglicherweise nicht aus, um alle softwarebasierten Tasks so zu optimieren, dass die Zeit- und Durchsatzvorgaben eingehalten werden. ⓘ

Methodologien

Systeme auf dem Chip werden mit Standard-Hardware-Verifikations- und Validierungstechniken modelliert, aber es werden zusätzliche Techniken verwendet, um SoC-Designalternativen zu modellieren und zu optimieren, damit das System im Hinblick auf die oben genannten Optimierungsziele optimal ist, und zwar unter Berücksichtigung einer Entscheidungsanalyse mit mehreren Kriterien. ⓘ

Task-Planung

Die Planung von Aufgaben ist eine wichtige Aufgabe in jedem Computersystem mit mehreren Prozessen oder Threads, die sich einen einzelnen Prozessorkern teilen. Es ist wichtig, die § Latenzzeit zu reduzieren und den § Durchsatz für eingebettete Software zu erhöhen, die auf den § Prozessorkernen eines SoCs läuft. Nicht jede wichtige Rechenaktivität in einem SoC wird in Software ausgeführt, die auf On-Chip-Prozessoren läuft, aber die Planung kann die Leistung von softwarebasierten Aufgaben und anderen Aufgaben, die gemeinsam genutzte Ressourcen betreffen, drastisch verbessern. ⓘ

SoCs planen Aufgaben oft nach Netzwerk-Scheduling und randomisierten Scheduling-Algorithmen. ⓘ

Pipelining

Hardware- und Software-Tasks werden bei der Entwicklung von Prozessoren häufig in einer Pipeline zusammengefasst. Pipelining ist ein wichtiges Prinzip zur Beschleunigung in der Computerarchitektur. Sie werden häufig in GPUs (Grafikpipeline) und RISC-Prozessoren (Weiterentwicklungen der klassischen RISC-Pipeline) eingesetzt, finden aber auch bei anwendungsspezifischen Aufgaben wie digitaler Signalverarbeitung und Multimedia-Manipulationen im Rahmen von SoCs Anwendung. ⓘ

Probabilistische Modellierung

SoCs werden häufig durch probabilistische Modelle, Warteschlangentheorie § Warteschlangennetzwerke und Markov-Ketten analysiert. Mit dem Little'schen Gesetz können beispielsweise SoC-Zustände und NoC-Puffer als Ankunftsprozesse modelliert und durch Poisson-Zufallsvariablen und Poisson-Prozesse analysiert werden. ⓘ

Markov-Ketten

SoCs werden häufig mit Markov-Ketten modelliert, sowohl mit zeitdiskreten als auch mit zeitkontinuierlichen Varianten. Die Modellierung von Markov-Ketten ermöglicht eine asymptotische Analyse der stationären Verteilung von Strom, Wärme, Latenz und anderen Faktoren des SoC, um Designentscheidungen für den allgemeinen Fall optimieren zu können. ⓘ

Fabrikation

SoC-Chips werden in der Regel in Metall-Oxid-Halbleiter-Technologie (MOS) hergestellt. Die oben beschriebenen Netzlisten werden als Grundlage für den physikalischen Designfluss (Place and Route) verwendet, um die Absichten des Designers in das Design des SoCs zu übertragen. Während dieses Konvertierungsprozesses wird das Design mit statischen Timing-Modellen, Simulationen und anderen Tools analysiert, um sicherzustellen, dass es die spezifizierten Betriebsparameter wie Frequenz, Stromverbrauch und -verlust, funktionale Integrität (wie im Code der Registerübertragungsebene beschrieben) und elektrische Integrität erfüllt. ⓘ

Wenn alle bekannten Fehler behoben sind und diese erneut überprüft wurden und alle physischen Entwurfsprüfungen erfolgt sind, werden die physischen Entwurfsdateien, die jede Schicht des Chips beschreiben, an die Maskenwerkstatt der Gießerei geschickt, wo ein vollständiger Satz von lithografischen Glasmasken geätzt wird. Diese werden an eine Wafer-Fertigungsanlage geschickt, um die SoC-Würfel vor der Verpackung und Prüfung herzustellen. ⓘ

SoCs können mit verschiedenen Technologien hergestellt werden, darunter:

- Vollständig kundenspezifischer ASIC

- Standardzellen-ASIC

- Feldprogrammierbares Gate-Array (FPGA) ⓘ

ASICs verbrauchen weniger Strom und sind schneller als FPGAs, können aber nicht umprogrammiert werden und sind teuer in der Herstellung. FPGA-Entwürfe eignen sich besser für Entwürfe mit geringerem Volumen, aber nach einer ausreichenden Anzahl von Produktionseinheiten reduzieren ASICs die Gesamtbetriebskosten. ⓘ

SoC-Designs verbrauchen weniger Strom und sind kostengünstiger und zuverlässiger als die Multichip-Systeme, die sie ersetzen. Da das System weniger Gehäuse enthält, sinken auch die Montagekosten. ⓘ

Wie bei den meisten VLSI-Designs (Very Large Scale Integration) sind jedoch die Gesamtkosten für einen großen Chip höher als für die gleiche Funktionalität, die auf mehrere kleinere Chips verteilt ist, da die Ausbeute geringer und die einmaligen Entwicklungskosten höher sind. ⓘ

Wenn es nicht möglich ist, einen SoC für eine bestimmte Anwendung zu konstruieren, ist eine Alternative ein System in Package (SiP), das eine Reihe von Chips in einem einzigen Gehäuse umfasst. Werden SoC in großen Mengen hergestellt, sind sie kostengünstiger als SiP, da ihre Verpackung einfacher ist. Ein weiterer Grund für die Bevorzugung von SiP ist die Tatsache, dass die Abwärme in einem SoC für einen bestimmten Zweck zu hoch sein kann, weil die funktionalen Komponenten zu nahe beieinander liegen, während in einem SiP die Wärme besser von den verschiedenen funktionalen Modulen abgeleitet wird, da sie räumlich weiter voneinander entfernt sind. ⓘ

Leistungsvergleiche

In der SoC-Forschung und -Entwicklung werden oft viele Optionen miteinander verglichen. Benchmarks, wie z. B. COSMIC, werden entwickelt, um solche Bewertungen zu unterstützen. ⓘ

Einsatzgebiet

Eingesetzt werden SoCs unter anderem in mobilen Geräten wie Smartphones, Tablet-Computer, sonstige Gadgets und Datenerfassungsgeräte, ebenso in der Steuerungs- und Automatisierungstechnik (z. B. Waschmaschine, Automobilelektronik, Industrieautomation) sowie in allen möglichen, vielen modernen Geräten der Unterhaltungselektronik. Meist sind viele verschiedene Schnittstellen zu bedienen (Sensoren, Aktoren, Netzwerke, Tasten, Anzeigen) und die Stückzahlen sind groß. Die Integration der Funktionen, die zuvor auf mehrere Bauelemente oder gar mehrere Leiterplatten verteilt waren, kann auch die Ausfall- und die Funktionale Sicherheit erhöhen, insbesondere wenn vielfältige Maßnahmen zur Fehleraufdeckung integriert sind, die mit diskreten Bauteilen nicht marktfähig zu realisieren wären. Für Anwendungen, die weniger große Stückzahlen generieren, wie in medizintechnischen Geräten oder der Avionik, werden selten speziell angepasste SoCs eingesetzt, sondern bleiben oft viele der integrierten Module ungenutzt. ⓘ

Debugging Interface

In der Regel besitzen SoCs eine Debug-Schnittstelle (englisch interface). Dies ist oft eine einfache RS-232-Schnittstelle, die häufig über USB emuliert wird. Sie bietet einen direkten Zugriff von außen auf zentrale Teile des SoC und ermöglicht es beispielsweise, im Betrieb von einer Terminalemulation aus Fehlermeldungen und allgemeine Informationen abzufragen. In komplexeren Umgebungen übernimmt diese Funktion oft auch eine JTAG-Schnittstelle. Diese wird typischerweise nicht nur zur Übertragung von Fehlermeldungen genutzt, sondern zur Kommunikation mit einem Hard- oder Softwaredebugmodul im SoC. Ein solches Modul erlaubt es dem Anwender, beispielsweise das SoC „anzuhalten“ und die Abarbeitung im CPU-Kern im Einzelschrittmodus („Step-by-Step“) durchzuführen und bei Bedarf währenddessen einzelne Registerwerte zu ändern oder beispielsweise eine Schleife abzukürzen oder einen Sprungbefehl zu umgehen. ⓘ

Eine weitere Anwendung dieser Schnittstelle ist das Programmieren programmierbarer Bereiche eines SoC, wie z. B. RAM, EEPROM, Flash oder auch einzelner Schaltungsteile bis hin zum gesamten SoC-Design (nur in einem FPGA o. Ä.). Meist hängen weitere externe Bausteine als „Kette“ an derselben JTAG-Schnittstelle, welche über einen sogenannten Boundary Scan angesprochen werden. ⓘ

Bus

Verbunden wird das System intern über einen oder mehrere Busse. In komplexeren SoCs kommt oft ein hierarchisches oder zumindest segmentiertes Bussystem zum Einsatz. Dieses besteht typischerweise aus einem schnellen Systembus, einem langsameren Peripheriebus und einem Register- bzw. Steuerbus. Schnelle Peripherieeinheiten werden mitunter aber auch direkt mit dem Systembus verbunden. Zwischen dem Systembus und dem Peripheriebus vermittelt eine Bridge. Weiterhin benötigt jeder Bus mit mehreren Mastern einen Arbiter. Für die besonders wichtige Verbindung zwischen dem Prozessor und seinem oder seinen Cache(s) bzw. einem kleinen lokalen Speicher wird oft ein proprietärer aber besonders schneller Prozessorbus eingesetzt. Ein Beispiel hierfür ist der LMB von Xilinx. ⓘ

Als Systembus sind in SoCs beispielsweise AMBA von Arm (Busse: AHB bzw. ASB/APB) CoreConnect von IBM (Busse: PLB/OPB/DCR) oder in jüngster Zeit auch der WishBone von Silicore/OpenCores.org stark vertreten. Weit verbreitet sind heute Busbreiten von 32 bis 128 Bit. Bei leistungsfähigen SoCs findet sich oft ein DMA-Controller am Systembus, um die CPU von Speicherzugriffen zu entlasten. ⓘ

Die Spezifikationen dieser Busse sind physikalisch alle auf die Implementierung in ASICs (anwendungsspezifischen integrierten Schaltungen) und/oder FPGAs (englisch Field Programmable Gate Array) ausgelegt und unterscheiden sich auch ansonsten stark von verbreiteten Systembussen wie PCI – beispielsweise wird auf Grund des festen Systemaufbaus im Allgemeinen kein Plug and Play verwendet. ⓘ

Taktgeber

Als Taktgeber und Zeitgeber sind Funktionsgruppen enthalten, die Impulse in einer bestimmten Frequenz abgeben. Es wird sich dabei um einfache physikalische Schwinger und weitere elektronische Funktionen zur Stabilisierung der Taktrate handeln, die für die Ablaufsteuerung und gegebenenfalls eine Synchronisation erforderlich sind. ⓘ

Eine Echtzeituhr (physikalische Uhr) empfängt oder misst und zählt lokal eine physikalische Zeit und kann ebenfalls enthalten sein. Dazu sind präzise physikalische Schwinger meist extern zum SoC angeordnet. ⓘ

Im weiteren Sinne sind mit dem Taktgeber außer dem Taktgeber und der Echtzeituhr auch spezielle stromsparende Weckschaltungen enthalten, die eine Uhrzeit auch nach Ausschalten des Systems behalten bzw. fortschreiben. Der oder die Taktgeber steuern dann auch den Bereitschaftszustand oder Sleep-Modus. ⓘ

Peripherie

Welche weiteren Peripherieeinheiten integriert werden, hängt sehr stark von der eigentlichen Anwendung, aber natürlich auch von vielen weiteren Faktoren wie den beim Prozessortyp erwähnten Kriterien ab. Diese Peripherieblöcke hängen meist nicht direkt am Systembus, sondern über eine sogenannte Bridge an einem separaten Peripheriebus. Dieser ist meist deutlich langsamer getaktet, genügt jedoch den Anforderungen der meisten Peripherie. Somit wird in erster Linie neben einigen anderen positiven Effekten die kapazitive Belastung des Systembusses gesenkt, und dieser kann somit schneller getaktet werden, was natürlich nur so lange hilft, bis die CPU tatsächlich auf eine Peripherieeinheit warten muss; dann sind im Normalfall beide Busse belegt, ohne etwas zu übertragen. Zusätzlich erleichtert ein Peripheriebus die Entwicklung einfacherer Komponenten, da die Integration dieses Bustyps im Gegensatz zum Systembus in der Regel deutlich leichter fällt und durch seine oft kleinere Bitbreite und langsamere Taktung deutlich geringere Anforderungen stellt. ⓘ

Je nach Art und Anzahl der Peripherieblöcke sowie Einsatzzweck des SoC enthält dieses manchmal einen dedizierten Interrupt Controller. Bei einfachen, kleineren oder besonders günstigen Systemen wird aber oft auf einen solchen Controller verzichtet, hier muss dann die Software die Interruptquelle ermitteln. Fortschrittliche Interrupt Controller bieten nicht nur viele Kanäle um die Zuordnung der Interrupts zu übernehmen, sondern bieten auch Kanäle mit unterschiedlichen Interrupt-Prioritäten an. Dies ist wichtig, wenn in Teilen des Systems Echtzeitanforderungen gestellt werden, die mit Interrupts nicht einfach bzw. manchmal überhaupt nicht zu lösen sind, da Interrupts nicht vorhersehbar sind. Dieses Problem kann oft durch eine intelligente Priorisierung gelöst werden. ⓘ

Oft sind weit mehr Peripherie-Module vorhanden, als in einer bestimmten Anwendung genutzt werden. Von den äußeren Anschlüssen bleiben weniger ungenutzt, da diese oft programmierbar verschiedenen Modulen zugeordnet werden können. Teilweise kann einzelnen Modulen der Takt und Gruppen von Modulen sogar die Spannung abgeschaltet werden, um die Leistungsaufnahme zu senken. ⓘ

Grafik

Viele SoCs enthalten auch einen Grafikprozessor, der ein oder mehrere Displays ansteuert. Hierfür ist in einem PC sonst eine separate Grafikkarte oder ein im Chipsatz integrierter Grafikkern (GPU) zuständig (sogenannte Hardwarebeschleunigung). Wegen der immer weiter fortschreitenden Integration fertigen seit einigen Jahren große CPU-Hersteller wie AMD/ATI, Intel und VIA/Nvidia, CPUs mit integrierten GPUs. Manche eingebetteten Systeme stellen hohe Anforderungen an die Grafikausgabe (Spielekonsolen, Blu-Ray/DVD-Player, bildgebende Geräte der Medizintechnik oder des Militärs), in anderen Fällen reichen oft LCDs oder einige Leuchtdioden zur Statusausgabe aus. Je nach Anwendung kann auch ganz auf eine grafische Ausgabe verzichtet werden. ⓘ

Besonders erschwert wird die Realisierung der Grafikfähigkeit oft durch besonders rigide Vorgaben bei maximaler Leistung, der maximalen Chipfläche oder auch durch einen extremen Preisdruck, sofern es sich um Massenware handelt. ⓘ

Audio

Ebenso anzutreffen sind in vielen SoCs spezielle Audiokerne. Diese werden beispielsweise in Mobiltelefonen, MP3-, DVD-Playern und ähnlichen Multimediageräten benötigt. Hierbei kommen je nach Anforderung, Stückzahl, finanziellen Möglichkeiten, Platzbeschränkungen usw. oft aber auch externe Hardware-Audio-Codecs zum Einsatz, welche dann nur über einen relativ kleinen IP-Block an den SoC-internen Bus angebunden sind. Sofern keine besonders hohen Anforderungen an die Audioqualität gestellt werden, kann beispielsweise ein AC’97-Codec zum Einsatz kommen. Kosten können mit solchen externen Komponenten aber nur bei kleinen Stückzahlen gespart werden, da sich hier die Entwicklungskosten für eine integrierte oder gar selbst entwickelte Lösung oft überproportional auswirken. ⓘ

Schnittstellen

SoCs kommunizieren typischerweise viel stärker mit ihrer technischen Umgebung als mit einem Bediener. Hierzu werden je nach Anforderung diverse Schnittstellen implementiert. Dies geschieht oftmals durch Einbinden fertiger IP-Blöcke, welche je nach Geschwindigkeit- und Latenzanforderung mit dem internen System- oder Peripheriebus verbunden werden. ⓘ

Zum Bediener hin kommt neben den bereits angesprochenen Audio- und Grafikschnittstellen hauptsächlich ein Tastaturcontroller (z. B. für Matrix-Tastaturen, serielle Tastaturen oder Touchpads) oder eine USB-Schnittstelle für entsprechende Geräte in Frage. Zur Kommunikation mit anderen Systemen kommen hauptsächlich Serielle Schnittstellen wie z. B. USB, RS232, CAN-Bus, LIN-Bus, MOST-Bus, ARINC 429 und Ethernet in Frage. Hierbei wird manchmal nur der MAC-Layer im SoC integriert, manchmal aber auch der PHY. Eine weitere Möglichkeit sind parallele Schnittstellen wie z. B. Centronics, Port-IO, IDE/CF usw. ⓘ

System-on-a-programmable-Chip

In zunehmender Zahl werden SoCs auf programmierbaren Chips implementiert, sogenannten System-on-a-programmable-Chips. Hierbei handelt es sich um eine Kombination aus FPGA-Logik und weiterer Peripherie sowie CPUs. Hierbei kommen als Prozessor sowohl sogenannte HardCores (im Silizium vorhandene CPU-Kerne parallel zur programmierbaren FPGA-Logik) als auch SoftCores (in den FPGA-Quellcode eingefügte, synthetisierbare CPU-Makros) zum Einsatz. Als HardCore gibt es beispielsweise PowerPC- oder ARM-Kerne, als SoftCores meist herstellerspezifische Prozessoren wie den MicroBlaze von Xilinx oder den NIOS II von Altera. Es existieren aber auch plattformunabhängige synthetisierbare Kerne von ARM, Lattice und anderen, welche entweder kommerziell als IP-Core vertrieben werden oder als Open Source zur Verfügung stehen. Auf diese Weise können die benötigten Funktionen eines Systems optimal auf die angebotenen Ressourcen verteilt werden. ⓘ

Nicht zu verwechseln ist dies mit Lösungen wie den PSoCs von Cypress oder anderen Firmen, bei welchen nur ein klassischer Mikrocontroller programmierbar ist, nicht jedoch dessen ALU und das ganze System mit Bussen, Speicher und weiterer Peripherie. ⓘ

Die üblichen Komponenten eines SoCs sind:

- Prozessor

- Register

- ALU

- Grafikprozessor

- Soundchip

- Speicher

- RAM

- ROM, z. B. als Flash- oder OTP-Speicher

- Speicher- und DMA-Controller

- Interne Einheiten

- Zeitgeber

- Zähler

- Interruptcontroller

- Watchdog-Timer

- Debug-Schnittstellen, z. B. JTAG

- Spezielle Recheneinheiten, wie z. B. in DSP-SoCs

- Kryptographie

- Peripherie-Einheiten und -Schnittstellen

- Tastaturcontroller, z. B. für Matrix-Tastaturen, serielle Tastaturen oder Touchpads

- Grafikschnittstellen, z. B. für LVDS, LCD, VGA, DVI, MPEG, HD/SDMI

- Serielle Schnittstellen, z. B. USB, RS232, CAN-Bus

- Parallele Schnittstellen, z. B. nach Centronics, Port-IO

- Pulsweitenmodulation, z. B. für DC-DC-Wandler oder Motorsteuerung

- Modulatoren, z. B. für GSM-Codierung, QAM, PSK

- Weitere Schnittstellen, z. B. Ethernet, MAC oder USB

- Analog-Digital-Umsetzer ⓘ

Hersteller

Am Markt finden sich zahlreiche Angebote für System-on-a-Chip-Halbleiter. Wichtige Anbieter hierfür sind: (alphabetisch sortiert, nicht nach Größe)

- ARM und Intel mit der ARM-Architektur bzw. der Weiterentwicklung XScale (auch Intel Quark oder Intel Edison)

- Altera, Microsemi und Xilinx mit diversen SoC-Plattformen in FPGAs

- Broadcom mit diversen Kommunikationschips

- Cypress Semiconductor Corporation für PSoC programmierbare System on Chip

- Infineon und NXP mit SoC-ICs für mobile Endgeräte wie Handys oder auch xDSL-Modems

- LSI Logic mit Chips für Netzwerk und Speicherprodukte

- MIPS und Lizenznehmer wie etwa AMD mit der AU1000 Serie

- Motorola/Freescale/NXP Semiconductors und IBM mit diversen PowerPC-Derivaten

- Qualcomm (Snapdragon) für moderne Smartphone-SoCs

- STMicroelectronics

- TDK-InvenSense mit SoC-ICs für Bewegung und Lage, Bild und Ton im Gamecontroller, Handy und Head-Mounted Display

- Texas Instruments mit OMAP, DSPs und RF-Modulen (z. B. ZigBee Modul µTiny) ⓘ