X86-Prozessor

| Designer | Intel, AMD |

|---|---|

| Bits | 16-Bit, 32-Bit und 64-Bit |

| Eingeführt | 1978 (16-Bit), 1985 (32-Bit), 2003 (64-Bit) |

| Aufbau | CISC |

| Typ | Register-Speicher |

| Kodierung | Variabel (1 bis 15 Bytes) |

| Verzweigung | Bedingungscode |

| Endianness | Wenig |

| Größe der Seite | 8086-i286: Keine i386, i486: 4 KB-Seiten P5 Pentium: zusätzliche 4 MB Seiten (Ältere PAE: 4 KB→2 MB) x86-64: 1 GB-Seiten hinzugefügt |

| Erweiterungen | x87, IA-32, x86-64, MMX, 3DNow! SSE, MCA, ACPI, SSE2, NX bit, SMT, SSE3, SSSE3, SSE4, SSE4.2, AES-NI, CLMUL, RDRAND, SHA, MPX, SME, SGX, XOP, F16C, ADX, BMI, FMA, AVX, AVX2, AVX-VNNI, AVX512, VT-x, VT-d, AMD-V, AMD-Vi, TSX, ASF, TXT |

| Offen | Teilweise. Für einige fortgeschrittene Funktionen kann für x86 eine Lizenz von Intel erforderlich sein; für x86-64 ist möglicherweise eine zusätzliche Lizenz von AMD erforderlich. Der 80486-Prozessor ist seit mehr als 30 Jahren auf dem Markt und kann daher nicht Gegenstand von Patentansprüchen sein. Die Vor-586er-Untergruppe der x86-Architektur ist daher völlig offen. |

| Register | |

| Allgemeiner Zweck |

|

| Fließkomma |

|

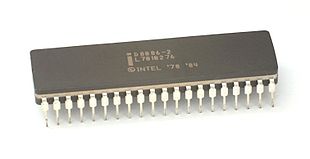

x86 ist eine Familie von CISC-Befehlssatzarchitekturen (Complex Instruction Set Computer), die ursprünglich von Intel auf der Grundlage des Intel-Mikroprozessors 8086 und seiner 8088-Variante entwickelt wurde. Der 8086 wurde 1978 als vollständige 16-Bit-Erweiterung des 8-Bit-Mikroprozessors 8080 von Intel eingeführt, mit Speichersegmentierung als Lösung für die Adressierung von mehr Speicher, als durch eine einfache 16-Bit-Adresse abgedeckt werden kann. Der Begriff "x86" entstand, weil die Namen mehrerer Nachfolger des 8086-Prozessors von Intel auf "86" enden, darunter die Prozessoren 80186, 80286, 80386 und 80486. ⓘ

Der Begriff ist nicht gleichbedeutend mit IBM-PC-Kompatibilität, da dies eine Vielzahl anderer Computerhardware einschließt. Eingebettete Systeme und Allzweckcomputer verwendeten x86-Chips, bevor der Markt für PC-kompatible Systeme entstand, einige von ihnen sogar vor dem Debüt des IBM PC (1981). ⓘ

Ab Juni 2022 basieren die meisten verkauften Desktop- und Laptop-Computer auf der x86-Architekturfamilie, während mobile Kategorien wie Smartphones oder Tablets von ARM dominiert werden. Im oberen Segment dominiert x86 weiterhin die rechenintensiven Workstation- und Cloud-Computing-Segmente. Der schnellste Supercomputer in der TOP500-Liste für Juni 2022 war das erste Exascale-System, Frontier, das mit AMD Epyc-CPUs auf der Grundlage des x86-ISA gebaut wurde; es durchbrach im Mai 2022 die 1-ExaFLOPS-Schwelle. ⓘ

x86 ist die Abkürzung einer Mikroprozessor-Architektur und der damit verbundenen Befehlssätze, welche unter anderem von den Chip-Herstellern Intel und AMD entwickelt werden. ⓘ

Die x86-Befehlssatzarchitektur (englisch Instruction Set Architecture, kurz „ISA“) ist nach den Prozessoren der 8086/8088-Reihe benannt, mit der sie 1978 eingeführt wurde. Die ersten Nachfolgeprozessoren wurden später mit 80186, 80286 usw. benannt. In den 1980er-Jahren war daher von der 80x86-Architektur die Rede – später wurde die „80“ am Anfang weggelassen. Die x86-Architektur erweiterte sich seither mit jeder Prozessorgeneration und war mit dem 80386 1985 bereits eine 32-Bit-Architektur, die explizit auch als i386 bezeichnet wurde. ⓘ

Da sich Ziffernkombinationen nicht markenrechtlich schützen lassen, gingen Intel und die meisten Mitbewerber nach Einführung des 80486 dazu über, Wortmarken wie Pentium oder Celeron (Intel) bzw. Athlon oder Phenom (AMD) zu verwenden, aber das alte Nummernschema blieb als Name der ganzen Familie erhalten. ⓘ

Überblick

In den 1980er und frühen 1990er Jahren, als die 8088 und 80286 noch weit verbreitet waren, stand der Begriff x86 in der Regel für jede 8086-kompatible CPU. Heute bedeutet x86 jedoch in der Regel eine binäre Kompatibilität auch mit dem 32-Bit-Befehlssatz des 80386. Das liegt daran, dass dieser Befehlssatz so etwas wie der kleinste gemeinsame Nenner für viele moderne Betriebssysteme geworden ist, und wahrscheinlich auch daran, dass der Begriff nach der Einführung des 80386 im Jahr 1985 üblich wurde. ⓘ

Einige Jahre nach der Einführung des 8086 und 8088 fügte Intel seinem Namensschema und seiner Terminologie eine gewisse Komplexität hinzu, als das "iAPX" des ehrgeizigen, aber erfolglosen Intel iAPX 432-Prozessors auf der erfolgreicheren 8086-Chipfamilie als eine Art Präfix auf Systemebene verwendet wurde. Ein 8086-System, einschließlich Koprozessoren wie 8087 und 8089 und einfacheren Intel-spezifischen Systemchips, wurde so als iAPX 86-System bezeichnet. Es gab auch die Bezeichnungen iRMX (für Betriebssysteme), iSBC (für Einplatinencomputer) und iSBX (für Multimodulplatinen auf Basis der 8086-Architektur), die alle unter dem Begriff Microsystem 80 zusammengefasst wurden. Dieses Bezeichnungsschema war jedoch nur von kurzer Dauer und galt für einige Jahre in den frühen 1980er Jahren. ⓘ

Obwohl der 8086 in erster Linie für eingebettete Systeme und kleine Mehrbenutzer- oder Einzelbenutzer-Computer entwickelt wurde, vor allem als Antwort auf den erfolgreichen 8080-kompatiblen Zilog Z80, wuchs die x86-Reihe bald an Funktionen und Verarbeitungsleistung. Heute ist x86 sowohl in stationären als auch in tragbaren Personal Computern allgegenwärtig und wird auch in Midrange-Computern, Workstations, Servern und den meisten neuen Supercomputer-Clustern der TOP500-Liste verwendet. Eine große Anzahl von Software, einschließlich einer großen Liste von x86-Betriebssystemen, verwendet x86-basierte Hardware. ⓘ

In eingebetteten Systemen ist der moderne x86-Prozessor jedoch relativ selten anzutreffen, und kleine Anwendungen mit geringem Stromverbrauch (die winzige Batterien verwenden) sowie Märkte für kostengünstige Mikroprozessoren, wie z. B. Haushaltsgeräte und Spielzeug, weisen keine nennenswerte x86-Präsenz auf. Einfache 8- und 16-Bit-basierte Architekturen sind hier üblich, obwohl die x86-kompatiblen VIA C7, VIA Nano, AMDs Geode, Athlon Neo und Intel Atom Beispiele für 32- und 64-Bit-Designs sind, die in einigen relativ stromsparenden und kostengünstigen Segmenten eingesetzt werden. ⓘ

Es gab mehrere Versuche, auch von Intel, die Marktdominanz der "uneleganten" x86-Architektur zu beenden, die direkt aus den ersten einfachen 8-Bit-Mikroprozessoren entwickelt wurde. Beispiele hierfür sind der iAPX 432 (ein Projekt, das ursprünglich den Namen Intel 8800 trug), der Intel 960, der Intel 860 und die Intel/Hewlett-Packard Itanium-Architektur. Aufgrund der ständigen Weiterentwicklung der x86-Mikroarchitekturen, der Schaltkreise und der Halbleiterfertigung wird es jedoch schwer sein, x86 in vielen Segmenten zu ersetzen. AMDs 64-Bit-Erweiterung von x86 (auf die Intel schließlich mit einem kompatiblen Design reagierte) und die Skalierbarkeit von x86-Chips in Form von modernen Multi-Core-CPUs unterstreichen x86 als Beispiel dafür, wie die kontinuierliche Verfeinerung etablierter Industriestandards der Konkurrenz durch völlig neue Architekturen widerstehen kann. ⓘ

Chronologie

In der folgenden Tabelle sind die Prozessormodelle und Modellreihen, die verschiedene Architekturen der x86-Familie implementieren, in chronologischer Reihenfolge aufgeführt. Jede Zeile ist durch deutlich verbesserte oder kommerziell erfolgreiche Prozessor-Mikroarchitekturen gekennzeichnet. ⓘ

| Ära | Einführung | Bekannte CPU-Modelle | Adressraum | Bemerkenswerte Merkmale | |||

|---|---|---|---|---|---|---|---|

| Linear | Virtuell | Physisch | |||||

| x86-16 | 1. | 1978 | Intel 8086, Intel 8088 (1979) | 16-Bit | NA | 20-Bit | 16-Bit ISA, IBM PC (8088), IBM PC/XT (8088) |

| 1982 | Intel 80186, Intel 80188 NEC V20/V30 (1983) |

8086-2 ISA, eingebettet (80186/80188) | |||||

| 2. | Intel 80286 und Klone | 30-Bit | 24-Bit | geschützter Modus, IBM PC/XT 286, IBM PC/AT | |||

| IA-32 | 3. | 1985 | Intel 80386, AMD Am386 (1991) | 32-Bit | 46-Bit | 32-Bit | 32-Bit ISA, Paging, IBM PS/2 |

| 4. (Pipelining, Cache) | 1989 | Intel 80486 Cyrix Cx486S, DLC (1992) AMD Am486 (1993), Am5x86 (1995) |

Pipelining, on-die x87 FPU (486DX), on-die Cache | ||||

| 5. (Superskalar) |

1993 | Intel Pentium, Pentium MMX (1996) | Superskalar, 64-Bit-Datenbus, schnellere FPU, MMX (Pentium MMX), APIC, SMP | ||||

| 1994 | NexGen Nx586 AMD 5k86/K5 (1996) |

Diskrete Mikroarchitektur (µ-op Übersetzung) | |||||

| 1995 | Cyrix Cx5x86 Cyrix 6x86/MX (1997)/MII (1998) |

dynamische Ausführung | |||||

| 6. (PAE, µ-op-Übersetzung) |

1995 | Intel Pentium Pro | 36-Bit (PAE) | µ-op-Übersetzung, bedingte Bewegungsbefehle, dynamische Ausführung, spekulative Ausführung, 3-Wege x86 superskalar, superskalare FPU, PAE, On-Chip L2-Cache | |||

| 1997 | Intel Pentium II, Pentium III (1999) Celeron (1998), Xeon (1998) |

On-Package (Pentium II) oder On-Die (Celeron) L2-Cache, SSE (Pentium III), Steckplatz 1, Sockel 370 oder Steckplatz 2 (Xeon) | |||||

| 1997 | AMD K6/K6-2 (1998)/K6-III (1999) | 32-Bit | 3DNow!, 3-stufiges Cache-System (K6-III) | ||||

| Verbesserte Plattform | 1999 | AMD Athlon Athlon XP/MP (2001) Duron (2000) Sempron (2004) |

36-Bit | MMX+, 3DNow!+, doppelt gepumpter Bus, Slot A oder Sockel A | |||

| 2000 | Transmeta Crusoe | 32-Bit | CMS-betriebener x86-Plattformprozessor, VLIW-128-Kern, On-Die-Speicher-Controller, On-Die-PCI-Brückenlogik | ||||

| Intel Pentium 4 | 36-Bit | SSE2, HTT (Northwood), NetBurst, quad-pumped bus, Trace Cache, Sockel 478 | |||||

| 2003 | Intel Pentium M Intel Kern (2006) Pentium Dual-Core (2007) |

µ-op fusion, XD bit (Dothan) (Intel Core "Yonah") | |||||

| Transmeta Efficeon | CMS 6.0.4, VLIW-256, NX-Bit, HT | ||||||

| IA-64 | 64-Bit-Übergang 1999-2005 |

2001 | Intel Itanium (2001-2017) | 52-Bit | 64-Bit-EPIC-Architektur, 128-Bit-VLIW-Befehlsbündel, IA-32-Hardware auf dem Chip, die x86-Betriebssysteme und x86-Anwendungen ermöglicht (frühe Generationen), IA-32-EL-Software, die x86-Anwendungen ermöglicht (Itanium 2), Itanium-Registerdateien werden auf x86-Register abgebildet | ||

| x86-64 | 64-Bit erweitert seit 2001 |

x86-64 ist die erweiterte 64-Bit-Architektur von x86, ihr Legacy-Modus bewahrt die gesamte und unveränderte x86-Architektur. Die native Architektur von x86-64-Prozessoren: Sie befindet sich im 64-Bit-Modus, hat keinen Zugriffsmodus bei der Segmentierung und bietet einen linearen Adressraum mit 64-Bit-Architektur-Permit; eine angepasste IA-32-Architektur, die sich im Kompatibilitätsmodus neben dem 64-Bit-Modus befindet, unterstützt die meisten x86-Anwendungen | |||||

| 2003 | Athlon 64/FX/X2 (2005), Opteron Sempron (2004)/X2 (2008) Turion 64 (2005)/X2 (2006) |

40-Bit | AMD64 (mit Ausnahme einiger Sempron-Prozessoren, die als reine x86-Prozessoren präsentiert werden), On-Die-Speicher-Controller, HyperTransport, On-Die-Dual-Core (X2), AMD-V (Athlon 64 Orleans), Sockel 754/939/940 oder AM2 | ||||

| 2004 | Pentium 4 (Prescott) Celeron D, Pentium D (2005) |

36-Bit | EM64T (aktiviert bei ausgewählten Modellen von Pentium 4 und Celeron D), SSE3, 2nd gen. NetBurst Pipelining, Dual-Core (On-Die: Pentium D 8xx, On-Chip: Pentium D 9xx), Intel VT (Pentium 4 6x2), Sockel LGA 775 | ||||

| 2006 | Intel Kern 2 Pentium Dual-Core (2007) Celeron Dual-Core (2008) |

Intel 64 (<<== EM64T), SSSE3(65 nm), breite dynamische Ausführung, µ-op fusion, macro-op fusion im 16-bit und 32-bit Modus, on-chip quad-core(Core 2 Quad), Smart Shared L2 Cache (Intel Core 2 "Merom") | |||||

| 2007 | AMD Phenom/II (2008) Athlon II (2009) Turion II (2009) |

48-Bit | Monolithischer Quad-Core (X4)/Triple-Core (X3), SSE4a, Rapid Virtualization Indexing (RVI), HyperTransport 3, AM2+ oder AM3 | ||||

| 2008 | Intel Core 2 (45 nm) | 40-Bit | SSE4.1 | ||||

| Intel Atom | Netbook- oder stromsparender Smart-Device-Prozessor, P54C-Kern wiederverwendet | ||||||

| Intel Kern i7 Kern i5 (2009) Kern i3 (2010) |

QuickPath, On-Chip-GMCH (Clarkdale), SSE4.2, Extended Page Tables (EPT) für Virtualisierung, Makro-Operations-Fusion im 64-Bit-Modus, (Intel Xeon "Bloomfield" mit Nehalem-Mikroarchitektur) | ||||||

| VIA Nano | hardwarebasierte Verschlüsselung; adaptive Energieverwaltung | ||||||

| 2010 | AMD FX | 48-Bit | Octa-Core, CMT (Clustered Multi-Thread), FMA, OpenCL, AM3+ | ||||

| 2011 | AMD APU A- und E-Serie (Llano) | 40-Bit | On-Die GPGPU, PCI Express 2.0, Sockel FM1 | ||||

| AMD APU C-, E- und Z-Reihe (Bobcat) | 36-Bit | APU für intelligente Geräte mit niedrigem Stromverbrauch | |||||

| Intel Core i3, Core i5 und Core i7 (Sandy Bridge/Ivy Bridge) |

Interne Ringverbindung, dekodierter µ-op-Cache, Sockel LGA 1155 | ||||||

| 2012 | AMD APU A-Serie (Bulldozer, Trinity und später) | 48-Bit | AVX, Bulldozer-basierte APU, Sockel FM2 oder Sockel FM2+ | ||||

| Intel Xeon Phi (Knights Corner) | PCI-E-Zusatzkarten-Coprozessor für XEON-basierte Systeme, Manycore Chip, In-Order P54C, sehr breite VPU (512-Bit SSE), LRBni-Befehle (8× 64-Bit) | ||||||

| 2013 | AMD Jaguar (Athlon, Sempron) |

SoC, Spielekonsole und stromsparender Prozessor für intelligente Geräte | |||||

| Intel Silvermont (Atom, Celeron, Pentium) |

36-Bit | SoC, Prozessor für intelligente Geräte mit niedrigem/ultra-niedrigem Stromverbrauch | |||||

| Intel Core i3, Core i5 und Core i7 (Haswell/Broadwell) | 39-Bit | AVX2-, FMA3-, TSX-, BMI1- und BMI2-Befehle, Sockel LGA 1150 | |||||

| 2015 | Intel Broadwell-U (Intel Core i3, Core i5, Core i7, Core M, Pentium, Celeron) |

SoC, On-Chip Broadwell-U PCH-LP (Multi-Chip-Modul) | |||||

| 2015−2020 | Intel Skylake/Kaby Lake/Cannon Lake/Coffee Lake/Rocket Lake (Intel Pentium/Celeron Gold, Core i3, Core i5, Core i7, Core i9) |

46-Bit | AVX-512 (beschränkt auf Cannon Lake-U und Workstation/Server-Varianten von Skylake) | ||||

| 2016 | Intel Xeon Phi (Knights Landing) | 48-Bit | Manycore-CPU und Coprozessor für Xeon-Systeme, Airmont (Atom) basierter Kern | ||||

| 2016 | AMD Bristol Ridge (AMD (Pro) A6/A8/A10/A12) |

Integrierter FCH auf dem Chip, SoC, Sockel AM4 | |||||

| 2017 | AMD Ryzen-Reihe/AMD Epyc-Reihe | AMDs Implementierung von SMT, On-Chip-Multi-Dies | |||||

| 2017 | Zhaoxin WuDaoKou (KX-5000, KH-20000) | Die erste brandneue x86-64-Architektur von Zhaoxin | |||||

| 2018−2021 | Intel Sunny Cove (Ice Lake-U und Y), Cypress Cove (Rocket Lake) | 57-Bit | Intels erste Implementierung von AVX-512 für das Verbrauchersegment. Hinzufügen von Vector Neural Network Instructions (VNNI) | ||||

| 2020 | Intel Willow Cove (Tiger Lake-Y/U/H) | Dual-Ring-Interconnect-Architektur, aktualisierter Gaussian Neural Accelerator (GNA2), neue AVX-512 Vector Intersection Instructions, Hinzufügung der Control-Flow Enforcement Technology (CET) | |||||

| 2021 | Intel Alder Lake | Hybrid-Design mit Leistungs- (Golden Cove) und Effizienzkernen (Gracemont), Unterstützung für PCIe Gen5 und DDR5, aktualisierter Gaussian Neural Accelerator (GNA3) | |||||

| Ära | Einführung | Bekannte CPU-Modelle | Adressraum | Bemerkenswerte Merkmale | |||

Geschichte

Konstrukteure und Hersteller

Zu verschiedenen Zeiten begannen Unternehmen wie IBM, VIA, NEC, AMD, TI, STM, Fujitsu, OKI, Siemens, Cyrix, Intersil, C&T, NexGen, UMC und DM&P mit der Entwicklung oder Herstellung von x86-Prozessoren (CPUs) für Personal Computer und eingebettete Systeme. Andere Unternehmen, die x86- oder x87-Prozessoren entwickelten oder herstellten, waren ITT Corporation, National Semiconductor, ULSI System Technology und Weitek. ⓘ

Solche x86-Implementierungen waren selten einfache Kopien, sondern verwendeten oft unterschiedliche interne Mikroarchitekturen und unterschiedliche Lösungen auf elektronischer und physikalischer Ebene. Natürlich waren die ersten kompatiblen Mikroprozessoren 16-Bit-Prozessoren, während 32-Bit-Designs erst viel später entwickelt wurden. Für den Personalcomputermarkt wurden um 1990 mit den i386- und i486-kompatiblen Prozessoren, die oft ähnlich wie die ursprünglichen Chips von Intel benannt wurden, echte Stückzahlen entwickelt. ⓘ

Nach dem i486 mit vollem Pipelining führte Intel 1993 den Markennamen Pentium (der im Gegensatz zu den Zahlen als Warenzeichen geschützt werden konnte) für seine neue Reihe superskalarer x86-Designs ein. Da das x86-Namensschema nun rechtlich geklärt war, mussten andere x86-Anbieter andere Namen für ihre x86-kompatiblen Produkte wählen, und anfangs entschieden sich einige dafür, mit Variationen des Nummerierungsschemas weiterzumachen: IBM ging eine Partnerschaft mit Cyrix ein, um die 5x86- und dann die sehr effizienten 6x86- (M1) und 6x86MX- (MII) Serien von Cyrix-Designs zu produzieren, die die ersten x86-Mikroprozessoren waren, die eine Registerumbenennung implementierten, um spekulative Ausführung zu ermöglichen. ⓘ

AMD entwickelte und produzierte in der Zwischenzeit den fortschrittlichen, aber verspäteten 5k86 (K5), der intern eng an AMDs früheres 29K-RISC-Design angelehnt war. Ähnlich wie der Nx586 von NexGen verwendete er eine Strategie, bei der dedizierte Pipeline-Stufen x86-Befehle in einheitliche und leicht zu handhabende Mikrooperationen dekodieren, eine Methode, die bis heute die Grundlage für die meisten x86-Designs ist. ⓘ

Einige frühe Versionen dieser Mikroprozessoren hatten Probleme mit der Wärmeableitung. Der 6x86 war auch von einigen kleineren Kompatibilitätsproblemen betroffen, dem Nx586 fehlte eine Gleitkommaeinheit (FPU) und (die damals entscheidende) Pin-Kompatibilität, während der K5 bei seiner (späteren) Einführung eine etwas enttäuschende Leistung aufwies. ⓘ

Die Unkenntnis der Kunden über Alternativen zur Pentium-Reihe trug ebenfalls dazu bei, dass diese Entwicklungen vergleichsweise erfolglos blieben, obwohl der K5 eine sehr gute Pentium-Kompatibilität aufwies und der 6x86 bei Integer-Code deutlich schneller war als der Pentium. Später gelang es AMD, sich mit der K6-Prozessorreihe zu einem ernsthaften Konkurrenten zu entwickeln, aus der die sehr erfolgreichen Athlon und Opteron hervorgingen. ⓘ

Es gab auch andere Konkurrenten, wie Centaur Technology (früher IDT), Rise Technology und Transmeta. Die energieeffizienten C3- und C7-Prozessoren von VIA Technologies, die von der Firma Centaur entwickelt wurden, wurden nach ihrer Veröffentlichung im Jahr 2005 viele Jahre lang verkauft. Der 2008 von Centaur entwickelte VIA Nano war ihr erster Prozessor mit superskalarer und spekulativer Ausführung. Er wurde etwa zur gleichen Zeit (2008) eingeführt, als Intel den Intel Atom vorstellte, seinen ersten "In-Order"-Prozessor nach dem P5 Pentium. ⓘ

Der ursprüngliche x86-Befehlssatz wurde im Laufe der Jahre durch zahlreiche Ergänzungen und Erweiterungen ergänzt, wobei fast durchgängig eine vollständige Abwärtskompatibilität gewährleistet wurde. Die Architekturfamilie wurde in Prozessoren von Intel, Cyrix, AMD, VIA Technologies und vielen anderen Unternehmen implementiert; es gibt auch offene Implementierungen, wie die Zet-SoC-Plattform (derzeit inaktiv). Dennoch besitzen nur Intel, AMD, VIA Technologies und DM&P Electronics Lizenzen für die x86-Architektur, und von diesen produzieren nur die ersten beiden aktiv moderne 64-Bit-Designs, was zu einem sogenannten "Duopol" von Intel und AMD bei x86-Prozessoren führt. ⓘ

Im Jahr 2014 begann jedoch das in Shanghai ansässige chinesische Unternehmen Zhaoxin, ein Joint Venture zwischen einem chinesischen Unternehmen und VIA Technologies, mit der Entwicklung von VIA-basierten x86-Prozessoren für Desktops und Laptops. Die Veröffentlichung seiner neuesten "7"-Familie von x86-Prozessoren (z. B. KX-7000), die zwar nicht ganz so schnell wie AMD- oder Intel-Chips sind, aber immer noch dem neuesten Stand der Technik entsprechen, war für 2021 geplant; bis März 2022 war die Veröffentlichung jedoch noch nicht erfolgt. ⓘ

Von der 16-Bit- und 32-Bit- zur 64-Bit-Architektur

Die Befehlssatzarchitektur wurde zweimal auf eine größere Wortgröße erweitert. Im Jahr 1985 brachte Intel den 32-Bit-Chip 80386 (später als i386 bekannt) heraus, der in den folgenden Jahren die früheren 16-Bit-Chips in Computern (wenn auch in der Regel nicht in eingebetteten Systemen) nach und nach ersetzte. Dieses erweiterte Programmiermodell wurde ursprünglich als i386-Architektur bezeichnet (wie seine erste Implementierung), aber Intel nannte es später IA-32, als es seine (nicht verwandte) IA-64-Architektur einführte. ⓘ

In den Jahren 1999-2003 erweiterte AMD diese 32-Bit-Architektur auf 64 Bit und bezeichnete sie in frühen Dokumenten als x86-64 und später als AMD64. Intel übernahm die Architekturerweiterungen von AMD bald unter dem Namen IA-32e, später unter dem Namen EM64T und schließlich unter Intel 64. Microsoft und Sun Microsystems/Oracle verwenden ebenfalls den Begriff "x64", während viele Linux-Distributionen und die BSDs auch den Begriff "amd64" verwenden. Microsoft Windows beispielsweise bezeichnet seine 32-Bit-Versionen als "x86" und seine 64-Bit-Versionen als "x64", während die Installationsdateien von 64-Bit-Windows-Versionen in einem Verzeichnis namens "AMD64" abgelegt werden müssen. ⓘ

Grundlegende Eigenschaften der Architektur

Die x86-Architektur ist eine Architektur mit variabler Befehlslänge, in erster Linie ein "CISC"-Design mit Schwerpunkt auf Abwärtskompatibilität. Der Befehlssatz ist jedoch nicht typisch CISC, sondern im Grunde eine erweiterte Version der einfachen Acht-Bit-Architekturen 8008 und 8080. Die Byte-Adressierung ist aktiviert, und die Wörter werden im Speicher in Little-Endian-Byte-Reihenfolge gespeichert. Der Speicherzugriff auf nicht vorzeichenbehaftete Adressen ist für fast alle Befehle zulässig. Die größte native Größe für Ganzzahlarithmetik und Speicheradressen (oder Offsets) beträgt je nach Architekturgeneration 16, 32 oder 64 Bit (neuere Prozessoren unterstützen auch kleinere Ganzzahlen). Mehrere skalare Werte können gleichzeitig über die SIMD-Einheit verarbeitet werden, die in späteren Generationen vorhanden ist (siehe unten). Unmittelbare Adressierungsoffsets und unmittelbare Daten können als 8-Bit-Mengen für die häufig auftretenden Fälle oder Kontexte ausgedrückt werden, in denen ein Bereich von -128..127 ausreicht. Typische Anweisungen sind daher 2 oder 3 Byte lang (obwohl einige viel länger sind und einige nur ein Byte umfassen). ⓘ

Um weiteren Kodierungsraum zu sparen, werden die meisten Register in Opcodes mit drei oder vier Bits ausgedrückt, letzteres über ein Opcode-Präfix im 64-Bit-Modus, während höchstens ein Operand einer Anweisung eine Speicherstelle sein kann. Dieser Speicheroperand kann jedoch auch das Ziel (oder eine Kombination aus Quelle und Ziel) sein, während der andere Operand, die Quelle, entweder ein Register oder ein Direktwert sein kann. Dies trägt unter anderem zu einer Codegröße bei, die mit der von Acht-Bit-Maschinen konkurriert, und ermöglicht eine effiziente Nutzung des Befehls-Cache-Speichers. Die relativ geringe Anzahl allgemeiner Register (ebenfalls ein Erbe der 8-Bit-Maschinen) hat die registerrelative Adressierung (unter Verwendung kleiner Immediate Offsets) zu einer wichtigen Methode für den Zugriff auf Operanden gemacht, insbesondere auf den Stack. Es wurde daher viel Arbeit investiert, um solche Zugriffe so schnell wie Registerzugriffe zu machen, d. h. einen Befehlsdurchsatz von einem Zyklus in den meisten Fällen, in denen die Daten, auf die zugegriffen wird, im Cache der obersten Ebene verfügbar sind. ⓘ

Fließkomma und SIMD

Für den ursprünglichen 8086 wurde ein spezieller Fließkommaprozessor mit internen 80-Bit-Registern, der 8087, entwickelt. Dieser Mikroprozessor wurde später zum erweiterten 80387 weiterentwickelt, und spätere Prozessoren enthielten eine abwärtskompatible Version dieser Funktionalität auf demselben Mikroprozessor wie der Hauptprozessor. Darüber hinaus enthalten moderne x86-Designs auch eine SIMD-Einheit (siehe SSE unten), in der Befehle parallel auf (einem oder zwei) 128-Bit-Wörtern arbeiten können, die jeweils zwei oder vier Gleitkommazahlen (jeweils 64 bzw. 32 Bit breit) oder alternativ 2, 4, 8 oder 16 Ganzzahlen (jeweils 64, 32, 16 oder 8 Bit breit) enthalten. ⓘ

Das Vorhandensein breiter SIMD-Register bedeutet, dass bestehende x86-Prozessoren bis zu 128 Bit Speicherdaten in einem einzigen Befehl laden oder speichern und auch bitweise Operationen (allerdings keine Ganzzahlarithmetik) auf vollen 128-Bit-Mengen parallel durchführen können. Die Sandy Bridge-Prozessoren von Intel fügten die AVX-Befehle (Advanced Vector Extensions) hinzu, die die SIMD-Register auf 256 Bit erweitern. Die Intel Initial Many Core Instructions, die von den Knights Corner Xeon Phi-Prozessoren implementiert wurden, und die AVX-512-Befehle, die von den Knights Landing Xeon Phi-Prozessoren und den Skylake-X-Prozessoren implementiert wurden, verwenden 512 Bit breite SIMD-Register. ⓘ

Aktuelle Implementierungen

Während der Ausführung verwenden aktuelle x86-Prozessoren einige zusätzliche Dekodierungsschritte, um die meisten Befehle in kleinere Teile, so genannte Mikrooperationen, aufzuteilen. Diese werden dann an eine Steuereinheit übergeben, die sie gemäß der x86-Semantik puffert und zeitlich einteilt, so dass sie von einer von mehreren (mehr oder weniger spezialisierten) Ausführungseinheiten teilweise parallel ausgeführt werden können. Diese modernen x86-Designs sind also pipelined, superskalar und auch in der Lage, außer der Reihe und spekulativ auszuführen (durch Verzweigungsvorhersage, Registerumbenennung und Vorhersage der Speicherabhängigkeit), was bedeutet, dass sie mehrere (teilweise oder vollständige) x86-Befehle gleichzeitig ausführen können, und zwar nicht unbedingt in der gleichen Reihenfolge wie im Befehlsstrom angegeben. Einige Intel-CPUs (Xeon Foster MP, einige Pentium 4 und einige Nehalem- und spätere Intel Core-Prozessoren) und AMD-CPUs (ab Zen) sind auch zum gleichzeitigen Multithreading mit zwei Threads pro Kern in der Lage (Xeon Phi hat vier Threads pro Kern). Einige Intel-CPUs unterstützen transaktionalen Speicher (TSX). ⓘ

Bei ihrer Einführung Mitte der 1990er Jahre wurde diese Methode manchmal als "RISC-Kern" oder "RISC-Übersetzung" bezeichnet, teilweise aus Marketinggründen, aber auch, weil diese Mikrooperationen einige Eigenschaften mit bestimmten Arten von RISC-Anweisungen gemeinsam haben. Aber auch der herkömmliche Mikrocode (der seit den 1950er Jahren verwendet wird) weist von Natur aus viele der gleichen Eigenschaften auf; die neue Methode unterscheidet sich hauptsächlich dadurch, dass die Übersetzung in Mikrooperationen nun asynchron erfolgt. Dadurch, dass die Ausführungseinheiten nicht mehr mit den Dekodierschritten synchronisiert werden müssen, eröffnen sich Möglichkeiten für eine umfassendere Analyse des (gepufferten) Codestroms, und es können somit Operationen erkannt werden, die parallel ausgeführt werden können und gleichzeitig mehr als eine Ausführungseinheit speisen. ⓘ

Die neuesten Prozessoren tun gegebenenfalls auch das Gegenteil; sie kombinieren bestimmte x86-Sequenzen (z. B. einen Vergleich gefolgt von einem bedingten Sprung) zu einer komplexeren Mikro-Operation, die besser zum Ausführungsmodell passt und daher schneller oder mit weniger Maschinenressourcen ausgeführt werden kann. ⓘ

Eine weitere Möglichkeit, die Leistung zu verbessern, besteht darin, die dekodierten Mikrooperationen zwischenzuspeichern, so dass der Prozessor direkt auf die dekodierten Mikrooperationen aus einem speziellen Cache zugreifen kann, anstatt sie erneut zu dekodieren. Intel verfolgte diesen Ansatz mit der Execution Trace Cache-Funktion in seiner NetBurst-Mikroarchitektur (für Pentium 4-Prozessoren) und später mit dem Decoded Stream Buffer (für Core-Prozessoren seit Sandy Bridge). ⓘ

Transmeta verwendete bei seinen Crusoe-x86-kompatiblen CPUs eine völlig andere Methode. Sie verwendeten Just-in-Time-Übersetzung, um x86-Befehle in den nativen VLIW-Befehlssatz der CPU zu konvertieren. Transmeta argumentiert, dass ihr Ansatz energieeffizientere Designs ermöglicht, da die CPU auf den komplizierten Dekodierungsschritt traditioneller x86-Implementierungen verzichten kann. ⓘ

Adressierungsmodi

Die Adressierungsmodi für 16-Bit-Prozessor-Modi lassen sich mit der folgenden Formel zusammenfassen:

Die Adressierungsmodi für 32-Bit-x86-Prozessor-Modi lassen sich durch die folgende Formel zusammenfassen:

Die Adressierungsmodi für den 64-Bit-Prozessormodus lassen sich durch die folgende Formel zusammenfassen:

Die relative Adressierung von Befehlen in 64-Bit-Code (RIP + Verschiebung, wobei RIP das Befehlszeigerregister ist) vereinfacht die Implementierung von positionsunabhängigem Code (wie in gemeinsam genutzten Bibliotheken in einigen Betriebssystemen verwendet). ⓘ

Der 8086 verfügte über 64 KB Acht-Bit-E/A-Speicher (oder alternativ 32 K-Worte mit 16 Bit) und einen 64 KB (ein Segment) großen Stack im Speicher, der von der Computerhardware unterstützt wurde. Auf den Stack können nur Wörter (zwei Byte) geschoben werden. Der Stack wächst zu numerisch niedrigeren Adressen hin, wobei SS:SP auf das zuletzt geschobene Element verweist. Es gibt 256 Interrupts, die sowohl von der Hardware als auch von der Software ausgelöst werden können. Die Interrupts können kaskadiert werden, wobei der Stack zum Speichern der Rücksprungadresse verwendet wird. ⓘ

x86-Register

16-Bit

Die ursprünglichen Intel 8086 und 8088 haben vierzehn 16-Bit-Register. Vier von ihnen (AX, BX, CX, DX) sind Allzweckregister (GPRs), obwohl jedes von ihnen einen zusätzlichen Zweck haben kann; zum Beispiel kann nur CX als Zähler mit dem Schleifenbefehl verwendet werden. Auf jedes Register kann als zwei getrennte Bytes zugegriffen werden (so kann auf das High-Byte von BX als BH und das Low-Byte als BL zugegriffen werden). Zwei Zeigerregister haben eine besondere Funktion: SP (Stack Pointer) zeigt auf die "Spitze" des Stacks, und BP (Base Pointer) wird oft verwendet, um auf eine andere Stelle im Stack zu zeigen, normalerweise über den lokalen Variablen (siehe Frame Pointer). Bei den Registern SI, DI, BX und BP handelt es sich um Adressregister, die auch zur Array-Indexierung verwendet werden können. ⓘ

Vier Segmentregister (CS, DS, SS und ES) werden verwendet, um eine Speicheradresse zu bilden. Das FLAGS-Register enthält Flags wie Carry-Flag, Overflow-Flag und Zero-Flag. Der Befehlszeiger (IP) schließlich verweist auf den nächsten Befehl, der aus dem Speicher geholt und dann ausgeführt wird; auf dieses Register kann ein Programm nicht direkt zugreifen (lesen oder schreiben). ⓘ

Die Intel 80186 und 80188 sind im Wesentlichen eine verbesserte 8086- bzw. 8088-CPU mit zusätzlichen On-Chip-Peripheriegeräten und verfügen über die gleichen CPU-Register wie die 8086 und 8088 (zusätzlich zu den Schnittstellenregistern für die Peripheriegeräte). ⓘ

Die Modelle 8086, 8088, 80186 und 80188 können einen optionalen Gleitkomma-Coprozessor, den 8087, verwenden. Der 8087 erscheint dem Programmierer als Teil der CPU und fügt acht 80-Bit breite Register, st(0) bis st(7), hinzu, von denen jedes numerische Daten in einem von sieben Formaten enthalten kann: 32-, 64- oder 80-Bit-Gleitkommazahlen, 16-, 32- oder 64-Bit (binäre) Ganzzahlen und 80-Bit gepackte dezimale Ganzzahlen. Es verfügt auch über ein eigenes 16-Bit-Statusregister, das über die Anweisung fntsw zugänglich ist, und es ist üblich, einige seiner Bits einfach für Verzweigungen zu verwenden, indem man sie in die normalen FLAGS kopiert. ⓘ

Beim Intel 80286 werden zur Unterstützung des geschützten Modus drei Spezialregister für Deskriptor-Tabellenadressen (GDTR, LDTR, IDTR) und ein viertes Taskregister (TR) für die Taskumschaltung verwendet. Der 80287 ist der Gleitkomma-Coprozessor für den 80286 und verfügt über die gleichen Register wie der 8087 mit den gleichen Datenformaten. ⓘ

32-Bit

Mit der Einführung des 32-Bit-Prozessors 80386 wurden die 16-Bit-Allzweckregister, Basisregister, Indexregister, Befehlszeiger und FLAGS-Register, nicht aber die Segmentregister, auf 32 Bit erweitert. Die Nomenklatur stellte dies dar, indem sie den Registernamen in der x86-Assemblersprache ein "E" (für "extended") voranstellte. So entspricht das AX-Register den untersten 16 Bits des neuen 32-Bit-Registers EAX, SI entspricht den untersten 16 Bits von ESI usw. Die Allzweckregister, Basisregister und Indexregister können alle als Basis in Adressierungsmodi verwendet werden, und alle diese Register außer dem Stapelzeiger können als Index in Adressierungsmodi verwendet werden. ⓘ

Zwei neue Segmentregister (FS und GS) wurden hinzugefügt. Mit einer größeren Anzahl von Registern, Befehlen und Operanden wurde das Maschinencodeformat erweitert. Um Abwärtskompatibilität zu gewährleisten, können Segmente mit ausführbarem Code so gekennzeichnet werden, dass sie entweder 16- oder 32-Bit-Anweisungen enthalten. Spezielle Präfixe ermöglichen die Aufnahme von 32-Bit-Anweisungen in ein 16-Bit-Segment und umgekehrt. ⓘ

Der 80386 hatte einen optionalen Gleitkomma-Coprozessor, den 80387; er hatte acht 80-Bit breite Register: st(0) bis st(7), wie der 8087 und 80287. Der 80386 konnte auch einen 80287-Coprozessor verwenden. Beim 80486 und allen nachfolgenden x86-Modellen ist die Fließkomma-Verarbeitungseinheit (FPU) auf dem Chip integriert. ⓘ

Mit dem Pentium MMX kamen acht 64-Bit-MMX-Integer-Vektorregister hinzu (MM0 bis MM7, die sich die unteren Bits mit dem 80-Bit breiten FPU-Stack teilen). Mit dem Pentium III fügte Intel ein 32-Bit-Streaming-SIMD-Extensions (SSE)-Steuer-/Statusregister (MXCSR) und acht 128-Bit-SSE-Gleitkommaregister (XMM0 bis XMM7) hinzu. ⓘ

64-Bit

Beginnend mit dem AMD Opteron-Prozessor hat die x86-Architektur die 32-Bit-Register auf 64-Bit-Register erweitert, und zwar auf ähnliche Weise wie bei der Erweiterung von 16 auf 32 Bit. Ein R-Präfix (für "Register") kennzeichnet die 64-Bit-Register (RAX, RBX, RCX, RDX, RSI, RDI, RBP, RSP, RFLAGS, RIP), und acht zusätzliche allgemeine 64-Bit-Register (R8-R15) wurden bei der Entwicklung von x86-64 ebenfalls eingeführt. Außerdem wurden acht weitere SSE-Vektor-Register (XMM8-XMM15) hinzugefügt. Diese Erweiterungen sind jedoch nur im 64-Bit-Modus nutzbar, einem der beiden Modi, die nur im Long-Modus verfügbar sind. Die Adressierungsmodi wurden gegenüber dem 32-Bit-Modus nicht grundlegend geändert, außer dass die Adressierung auf 64 Bit erweitert wurde, virtuelle Adressen nun auf 64 Bit erweitert sind (um Modusbits in virtuellen Adressen zu verbieten) und andere Selektordetails drastisch reduziert wurden. Außerdem wurde ein Adressierungsmodus hinzugefügt, der Speicherreferenzen relativ zu RIP (dem Befehlszeiger) erlaubt, um die Implementierung von positionsunabhängigem Code zu erleichtern, der in gemeinsam genutzten Bibliotheken in einigen Betriebssystemen verwendet wird. ⓘ

128-Bit

SIMD-Register XMM0-XMM15 (XMM0-XMM31, wenn AVX-512 unterstützt wird). ⓘ

256-Bit

SIMD-Register YMM0-YMM15 (YMM0-YMM31, wenn AVX-512 unterstützt wird). Die untere Hälfte jedes YMM-Registers wird auf das entsprechende XMM-Register abgebildet. ⓘ

512-Bit

SIMD-Register ZMM0-ZMM31. Die untere Hälfte jedes ZMM-Registers wird auf das entsprechende YMM-Register abgebildet. ⓘ

Sonstiges/Spezialzweck

x86-Prozessoren, die über einen geschützten Modus verfügen, d. h. der 80286 und spätere Prozessoren, haben auch drei Deskriptorregister (GDTR, LDTR, IDTR) und ein Taskregister (TR). ⓘ

32-Bit-x86-Prozessoren (beginnend mit dem 80386) enthalten auch verschiedene Spezial-/Verschiedene-Register wie Steuerregister (CR0 bis 4, CR8 nur für 64-Bit), Debug-Register (DR0 bis 3, plus 6 und 7), Testregister (TR3 bis 7; nur 80486) und modellspezifische Register (MSRs, erscheinen mit dem Pentium). ⓘ

AVX-512 hat acht zusätzliche 64-Bit-Maskenregister K0-K7 zur Auswahl von Elementen in einem Vektorregister. Je nach Vektorregister und Elementbreiten kann nur eine Teilmenge der Bits des Maskenregisters von einem bestimmten Befehl verwendet werden. ⓘ

Zweck

Obwohl die Hauptregister (mit Ausnahme des Befehlszeigers) in den 32-Bit- und 64-Bit-Versionen des Befehlssatzes "Allzweckregister" sind und für alles Mögliche verwendet werden können, war ursprünglich vorgesehen, dass sie für die folgenden Zwecke verwendet werden:

- AL/AH/AX/EAX/RAX: Akkumulator

- CL/CH/CX/ECX/RCX: Zähler (zur Verwendung mit Schleifen und Strings)

- DL/DH/DX/EDX/RDX: Erweiterung der Genauigkeit des Akkumulators (z. B. Kombination von 32-Bit-EAX und EDX für 64-Bit-Ganzzahloperationen in 32-Bit-Code)

- BL/BH/BX/EBX/RBX: Basisindex (zur Verwendung mit Arrays)

- SP/ESP/RSP: Stapelzeiger für die oberste Adresse des Stapels.

- BP/EBP/RBP: Stack-Basiszeiger, der die Adresse des aktuellen Stack-Frames enthält.

- SI/ESI/RSI: Quellindex für String-Operationen.

- DI/EDI/RDI: Zielindex für String-Operationen.

- IP/EIP/RIP: Anweisungszeiger. Enthält den Programmzähler, die Adresse der nächsten Anweisung. ⓘ

Segment-Register:

- CS: Code

- DS: Daten

- SS: Stapel

- ES: Extra Daten

- FS: Zusätzliche Daten #2

- GS: Zusätzliche Daten #3 ⓘ

Für die anderen 8 Register, die nur im 64-Bit-Modus verfügbar sind, wurden keine besonderen Zwecke vorgesehen. ⓘ

Einige Befehle lassen sich effizienter kompilieren und ausführen, wenn diese Register für ihren vorgesehenen Zweck verwendet werden. Die Verwendung von AL als Akkumulator und das Addieren eines unmittelbaren Byte-Wertes ergibt beispielsweise den effizienten Opcode 04h für "Add to AL", während die Verwendung des BL-Registers den allgemeinen und längeren Opcode 80C3h für "Add to Register" ergibt. Ein weiteres Beispiel ist die Division und Multiplikation mit doppelter Genauigkeit, die speziell mit den Registern AX und DX funktioniert. ⓘ

Moderne Compiler profitierten von der Einführung des sib-Bytes (scale-index-base byte), das eine einheitliche Behandlung von Registern ermöglicht (Minicomputer-ähnlich). Die generelle Verwendung des Sib-Bytes ist jedoch nicht optimal, da sie zu längeren Kodierungen führt, als wenn sie nur bei Bedarf selektiv verwendet wird. (Der Hauptvorteil des Sib-Bytes liegt in der Orthogonalität und den leistungsfähigeren Adressierungsmodi, die es ermöglichen, Anweisungen und die Verwendung von Registern für Adressberechnungen wie die Skalierung eines Indexes einzusparen.) Einige spezielle Befehle verloren im Hardware-Design an Priorität und wurden langsamer als gleichwertige kleine Codesequenzen. Ein bemerkenswertes Beispiel ist die Anweisung LODSW. ⓘ

Aufbau

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 ⓘ |

|---|---|---|---|---|---|---|---|

| R?X | |||||||

| E?X | |||||||

| ?X | |||||||

| ?H | ?L | ||||||

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 ⓘ |

|---|---|---|---|---|---|---|---|

| ? | |||||||

| ?D | |||||||

| ?W | |||||||

| ?B | |||||||

| 16 | 8 ⓘ |

|---|---|

| ?S | |

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 ⓘ |

|---|---|---|---|---|---|---|---|

| R?P | |||||||

| E?P | |||||||

| ?P | |||||||

| ?PL | |||||||

Hinweis: Die ?PL-Register sind nur im 64-Bit-Modus verfügbar. ⓘ

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 ⓘ |

|---|---|---|---|---|---|---|---|

| R?I | |||||||

| E?I | |||||||

| ?I | |||||||

| ?IL | |||||||

Hinweis: Die ?IL-Register sind nur im 64-Bit-Modus verfügbar. ⓘ

| 64 | 56 | 48 | 40 | 32 | 24 | 16 | 8 ⓘ |

|---|---|---|---|---|---|---|---|

| RIP | |||||||

| EIP | |||||||

| IP | |||||||

Betriebsarten

Real-Modus

Der Real-Adressmodus, allgemein als Real-Modus bezeichnet, ist ein Betriebsmodus von 8086- und späteren x86-kompatiblen CPUs. Der Real-Modus ist gekennzeichnet durch einen segmentierten 20-Bit-Speicheradressraum (was bedeutet, dass nur etwas mehr als 1 MiB Speicher adressiert werden kann), direkten Software-Zugriff auf periphere Hardware und kein Konzept für Speicherschutz oder Multitasking auf Hardware-Ebene. Alle x86-CPUs der Serie 80286 und später starten beim Einschalten im Real-Modus; 80186-CPUs und früher hatten nur einen Betriebsmodus, der bei späteren Chips dem Real-Modus entspricht. (Auf der IBM-PC-Plattform ist der direkte Software-Zugriff auf die IBM-BIOS-Routinen nur im Real-Modus möglich, da das BIOS für den Real-Modus geschrieben wurde. Dies ist jedoch keine Eigenschaft der x86-CPU, sondern des IBM-BIOS-Designs.) ⓘ

Um mehr als 64 KB Speicher nutzen zu können, müssen die Segmentregister verwendet werden. Dies führte zu großen Komplikationen für Compiler-Implementierer, die ungerade Zeigermodi wie "near", "far" und "huge" einführten, um die implizite Natur der segmentierten Architektur in unterschiedlichem Maße zu nutzen, wobei einige Zeiger 16-Bit-Offsets innerhalb implizierter Segmente und andere Zeiger Segmentadressen und Offsets innerhalb von Segmenten enthielten. Es ist technisch möglich, bis zu 256 KB Speicher für Code und Daten zu verwenden, mit bis zu 64 KB für Code, indem alle vier Segmentregister einmal gesetzt werden und dann nur 16-Bit-Offsets (optional mit Standard-Segment-Override-Präfixen) verwendet werden, um den Speicher zu adressieren, aber dies schränkt die Art und Weise, wie Daten adressiert und Speicheroperanden kombiniert werden können, erheblich ein und verstößt gegen die architektonische Absicht der Intel-Designer, die getrennte Datenelemente (z. z.B. Arrays, Strukturen, Code-Einheiten) in separaten Segmenten enthalten sein und über ihre eigenen Segmentadressen adressiert werden sollen, in neuen Programmen, die nicht von früheren 8-Bit-Prozessoren mit 16-Bit-Adressräumen portiert werden. ⓘ

Unreal-Modus

Der Unreal-Modus wird von einigen 16-Bit-Betriebssystemen und einigen 32-Bit-Bootloadern verwendet. ⓘ

Systemverwaltungsmodus

Der Systemverwaltungsmodus (SMM) wird nur von der Systemfirmware (BIOS/UEFI) verwendet, nicht aber von Betriebssystemen und Anwendungssoftware. Der SMM-Code wird im SMRAM ausgeführt. ⓘ

Geschützter Modus

Zusätzlich zum Real-Mode unterstützt der Intel 80286 den Protected-Mode, der den adressierbaren physikalischen Speicher auf 16 MB und den adressierbaren virtuellen Speicher auf 1 GB erweitert und einen geschützten Speicher bereitstellt, der verhindert, dass sich Programme gegenseitig beschädigen. Dies wird dadurch erreicht, dass die Segmentregister nur zum Speichern eines Index in einer Deskriptortabelle verwendet werden, die im Speicher abgelegt ist. Es gibt zwei solcher Tabellen, die Global Descriptor Table (GDT) und die Local Descriptor Table (LDT), die jeweils bis zu 8192 Segmentdeskriptoren enthalten, wobei jedes Segment Zugriff auf 64 KB Speicher ermöglicht. Beim 80286 liefert ein Segmentdeskriptor eine 24-Bit-Basisadresse, und diese Basisadresse wird zu einem 16-Bit-Offset addiert, um eine absolute Adresse zu erhalten. Die Basisadresse aus der Tabelle erfüllt die gleiche Funktion wie der literale Wert des Segmentregisters im Real-Mode; die Segmentregister wurden von direkten Registern in indirekte Register umgewandelt. Jedem Segment kann eine von vier Ringebenen zugewiesen werden, die für die hardwarebasierte Computersicherheit verwendet werden. Jeder Segmentdeskriptor enthält auch ein Segmentlimitfeld, das den maximalen Offset angibt, der für das Segment verwendet werden kann. Da die Offsets 16 Bit betragen, sind die Segmente im geschützten Modus 80286 immer noch auf jeweils 64 KB begrenzt. ⓘ

Jedes Mal, wenn ein Segmentregister im geschützten Modus geladen wird, muss der 80286 einen 6-Byte-Segmentdeskriptor aus dem Speicher in eine Reihe von versteckten internen Registern lesen. Daher ist das Laden von Segmentregistern im geschützten Modus viel langsamer als im realen Modus, und ein sehr häufiger Segmentwechsel ist zu vermeiden. Tatsächliche Speicheroperationen, die Segmente im geschützten Modus verwenden, werden nicht wesentlich verlangsamt, da der 80286 und spätere Modelle über Hardware verfügen, die den Offset parallel zur Befehlsausführung mit der Segmentgrenze vergleicht. ⓘ

Mit dem Intel 80386 wurden die Offsets und auch das Segmentlimitfeld in jedem Segmentdeskriptor auf 32 Bit erweitert, so dass ein Segment den gesamten Speicherbereich umfassen kann. Außerdem wurde im geschützten Modus die Unterstützung für Paging eingeführt, ein Mechanismus, der die Verwendung von ausgelagertem virtuellem Speicher (mit 4 KB Seitengröße) ermöglicht. Paging ermöglicht es der CPU, jede Seite des virtuellen Speicherbereichs auf jede Seite des physischen Speicherbereichs abzubilden. Dazu verwendet sie zusätzliche Abbildungstabellen im Speicher, so genannte Seitentabellen. Im geschützten Modus des 80386 kann Paging entweder aktiviert oder deaktiviert werden; der Segmentierungsmechanismus ist immer aktiv und erzeugt virtuelle Adressen, die dann durch den Paging-Mechanismus abgebildet werden, wenn dieser aktiviert ist. Der Segmentierungsmechanismus kann auch effektiv ausgeschaltet werden, indem alle Segmente eine Basisadresse von 0 und eine Größenbegrenzung auf den gesamten Adressraum haben; dies erfordert auch eine minimal dimensionierte Segmentdeskriptortabelle von nur vier Deskriptoren (da die FS- und GS-Segmente nicht verwendet werden müssen). ⓘ

Paging wird von modernen Multitasking-Betriebssystemen ausgiebig genutzt. Linux, 386BSD und Windows NT wurden für den 386er entwickelt, weil er die erste CPU mit Intel-Architektur war, die Paging und 32-Bit-Segmentoffsets unterstützte. Die 386-Architektur wurde zur Grundlage für alle weiteren Entwicklungen der x86-Serie. ⓘ

x86-Prozessoren, die den geschützten Modus unterstützen, booten aus Gründen der Abwärtskompatibilität mit der älteren 8086-Prozessorklasse in den Real-Mode. Beim Einschalten (auch als Booten bezeichnet) initialisiert sich der Prozessor im Real-Mode und beginnt dann mit der Ausführung von Befehlen. Der Boot-Code des Betriebssystems, der möglicherweise im Nur-Lese-Speicher gespeichert ist, kann den Prozessor in den geschützten Modus versetzen, um das Paging und andere Funktionen zu aktivieren). gelten nicht im geschützten Modus. Umgekehrt ist die Segmentarithmetik, eine gängige Praxis im Real-Mode-Code, im geschützten Modus nicht zulässig. ⓘ

Virtueller 8086-Modus

Es gibt auch einen Untermodus des geschützten 32-Bit-Modus (auch bekannt als geschützter 80386-Modus), den virtuellen 8086-Modus, der auch als V86-Modus bekannt ist. Dabei handelt es sich im Grunde um einen speziellen hybriden Betriebsmodus, in dem Programme und Betriebssysteme im realen Modus unter der Kontrolle eines Supervisor-Betriebssystems im geschützten Modus ausgeführt werden können. Dies ermöglicht ein hohes Maß an Flexibilität bei der gleichzeitigen Ausführung von Programmen im geschützten Modus und im realen Modus. Dieser Modus ist ausschließlich für die 32-Bit-Version des geschützten Modus verfügbar; es gibt ihn nicht in der 16-Bit-Version des geschützten Modus oder im langen Modus. ⓘ

Langer Modus

Mitte der 1990er Jahre wurde deutlich, dass der 32-Bit-Adressraum der x86-Architektur die Leistung bei Anwendungen, die große Datensätze benötigen, einschränkt. Mit einem 32-Bit-Adressraum konnte der Prozessor nur 4 GB an Daten direkt adressieren, eine Größe, die von Anwendungen wie Videoverarbeitung und Datenbank-Engines übertroffen wird. Mit 64-Bit-Adressen ist es möglich, 16 EiB an Daten direkt zu adressieren, obwohl die meisten 64-Bit-Architekturen den Zugriff auf den vollen 64-Bit-Adressraum nicht unterstützen; AMD64 beispielsweise unterstützt nur 48 Bits einer 64-Bit-Adresse, aufgeteilt in vier Paging-Ebenen. ⓘ

Im Jahr 1999 veröffentlichte AMD eine (fast) vollständige Spezifikation für eine 64-Bit-Erweiterung der x86-Architektur, die sie x86-64 nannten und angeblich produzieren wollten. Dieses Design wird derzeit in fast allen x86-Prozessoren verwendet, mit einigen Ausnahmen, die für eingebettete Systeme bestimmt sind. ⓘ

Massenproduzierte x86-64-Chips für den allgemeinen Markt waren vier Jahre später, im Jahr 2003, verfügbar, nachdem die Zeit für die Erprobung und Verfeinerung funktionierender Prototypen genutzt worden war; etwa zur gleichen Zeit wurde der ursprüngliche Name x86-64 in AMD64 geändert. Der Erfolg der AMD64-Prozessoren und die geringe Akzeptanz der IA-64-Architektur zwangen Intel, eine eigene Implementierung des AMD64-Befehlssatzes zu veröffentlichen. Intel hatte zuvor Unterstützung für AMD64 implementiert, entschied sich aber dagegen, in der Hoffnung, dass AMD AMD64 nicht auf den Markt bringen würde, bevor der neue IA-64-Befehlssatz des Itanium weithin angenommen war. Das Unternehmen bezeichnete seine AMD64-Implementierung als EM64T und benannte sie später in Intel 64 um. ⓘ

In der Literatur und in den Namen der Produktversionen bezeichnen Microsoft und Sun AMD64/Intel 64 in den Betriebssystemen Windows und Solaris gemeinsam als x64. Linux-Distributionen bezeichnen es entweder als "x86-64", seine Variante "x86_64" oder "amd64". BSD-Systeme verwenden "amd64", während macOS "x86_64" verwendet. ⓘ

Der lange Modus ist größtenteils eine Erweiterung des 32-Bit-Befehlssatzes, aber anders als beim Übergang von 16 auf 32 Bit wurden im 64-Bit-Modus viele Befehle weggelassen. Dies hat keine Auswirkungen auf die tatsächliche binäre Abwärtskompatibilität (bei der Legacy-Code in anderen Modi ausgeführt wird, die diese Befehle weiterhin unterstützen), aber es ändert die Arbeitsweise von Assemblern und Compilern für neuen Code. ⓘ

Dies war das erste Mal, dass eine größere Erweiterung der x86-Architektur von einem anderen Hersteller als Intel initiiert und initiiert wurde. Es war auch das erste Mal, dass Intel Technologie dieser Art von einer externen Quelle akzeptierte. ⓘ

Erweiterungen

Fließkomma-Einheit

Die frühen x86-Prozessoren konnten mit Fließkomma-Hardware in Form einer Reihe von numerischen Fließkomma-Koprozessoren mit Namen wie 8087, 80287 und 80387, abgekürzt x87, erweitert werden. Dies wurde auch als NPX (Numeric Processor eXtension) bezeichnet, eine treffende Bezeichnung, da die Koprozessoren zwar hauptsächlich für Fließkommaberechnungen verwendet wurden, aber auch ganzzahlige Operationen im binären und dezimalen Format durchführten. Mit wenigen Ausnahmen haben der 80486 und die nachfolgenden x86-Prozessoren diese x87-Funktionalität auf dem Chip integriert, wodurch die x87-Befehle de facto zu einem festen Bestandteil des x86-Befehlssatzes wurden. ⓘ

Jedes x87-Register, bekannt als ST(0) bis ST(7), ist 80 Bit breit und speichert Zahlen im IEEE-Gleitkomma-Standardformat mit doppelter erweiterter Genauigkeit. Diese Register sind als Stapel organisiert, wobei ST(0) an der Spitze steht. Dies wurde getan, um Opcode-Platz zu sparen, und die Register sind daher nur für einen der beiden Operanden in einem Register-zu-Register-Befehl zufällig zugänglich; ST0 muss immer einer der beiden Operanden sein, entweder die Quelle oder das Ziel, unabhängig davon, ob der andere Operand ST(x) oder ein Speicheroperand ist. Ein beliebiger Zugriff auf die Stapelregister kann jedoch durch einen Befehl erfolgen, der ein beliebiges ST(x) mit ST(0) austauscht. ⓘ

Zu den Operationen gehören arithmetische und transzendentale Funktionen, einschließlich trigonometrischer und exponentieller Funktionen, sowie Befehle, die gängige Konstanten (wie 0; 1; e, die Basis des natürlichen Logarithmus; log2(10); und log10(2)) in eines der Stapelregister laden. Die Fähigkeit zur Verarbeitung ganzer Zahlen wird zwar oft übersehen, aber der x87 kann mit einem einzigen Befehl größere ganze Zahlen verarbeiten als der 8086, 80286, 80386 oder jede andere x86-CPU ohne 64-Bit-Erweiterungen, und wiederholte ganzzahlige Berechnungen selbst mit kleinen Werten (z. B. 16-Bit) können beschleunigt werden, indem ganzzahlige Befehle auf der x86-CPU und dem x87 parallel ausgeführt werden. (Die x86-CPU läuft weiter, während der x87-Coprozessor rechnet, und der x87 setzt ein Signal an die x86-CPU, wenn er fertig ist, oder unterbricht die x86-CPU, wenn sie aufgrund eines Fehlers Hilfe benötigt). ⓘ

MMX

MMX ist ein SIMD-Befehlssatz, der von Intel entwickelt und 1997 für den Pentium MMX-Mikroprozessor eingeführt wurde. Der MMX-Befehlssatz wurde aus einem ähnlichen Konzept entwickelt, das erstmals auf dem Intel i860 verwendet wurde. Er wird von den meisten nachfolgenden IA-32-Prozessoren von Intel und anderen Anbietern unterstützt. MMX wird in der Regel für die Videoverarbeitung (z. B. in Multimedia-Anwendungen) verwendet. ⓘ

MMX fügte der Architektur 8 neue Register hinzu, die als MM0 bis MM7 bezeichnet werden (im Folgenden als MMn bezeichnet). In Wirklichkeit handelte es sich bei diesen neuen Registern nur um Aliase für die bestehenden x87-FPU-Stack-Register. Alles, was mit dem Fließkomma-Stack gemacht wurde, wirkte sich also auch auf die MMX-Register aus. Im Gegensatz zum FP-Stack waren diese MMn-Register fest, nicht relativ, und daher waren sie beliebig zugänglich. Der Befehlssatz hat die Stack-ähnliche Semantik nicht übernommen, so dass bestehende Betriebssysteme den Registerstatus beim Multitasking ohne Änderungen weiterhin korrekt speichern und wiederherstellen konnten. ⓘ

Jedes der MMn-Register ist eine 64-Bit-Ganzzahl. Eines der wichtigsten Konzepte des MMX-Befehlssatzes ist jedoch das Konzept der gepackten Datentypen, d. h. statt das gesamte Register für eine einzelne 64-Bit-Ganzzahl (Quadword) zu verwenden, kann man es für zwei 32-Bit-Ganzzahlen (Doubleword), vier 16-Bit-Ganzzahlen (Word) oder acht 8-Bit-Ganzzahlen (Byte) verwenden. Da die 64-Bit-MMn-Register des MMX dem FPU-Stack zugeordnet sind und jedes der Gleitkommaregister 80 Bit breit ist, sind die oberen 16 Bit der Gleitkommaregister im MMX unbenutzt. Diese Bits werden von jedem MMX-Befehl auf alle Einsen gesetzt, was der Gleitkommadarstellung von NaNs oder Unendlichkeiten entspricht. ⓘ

3DNow!

Im Jahr 1997 führte AMD 3DNow! ein. Die Einführung dieser Technologie fiel mit dem Aufkommen von 3D-Unterhaltungsanwendungen zusammen und sollte die Vektorverarbeitungsleistung der CPU bei grafikintensiven Anwendungen verbessern. Entwickler von 3D-Videospielen und Anbieter von 3D-Grafikhardware nutzen 3DNow!, um ihre Leistung auf AMDs Prozessorserien K6 und Athlon zu verbessern. ⓘ

3DNow! wurde als natürliche Weiterentwicklung von MMX von Ganzzahlen zu Fließkomma entwickelt. Als solches verwendet es genau die gleiche Registerbenennungskonvention wie MMX, d.h. MM0 bis MM7. Der einzige Unterschied besteht darin, dass anstelle von Ganzzahlen in diese Register zwei Gleitkommazahlen mit einfacher Genauigkeit in jedes Register gepackt werden. Der Vorteil des Aliasing der FPU-Register besteht darin, dass dieselben Befehls- und Datenstrukturen, die zum Speichern des Zustands der FPU-Register verwendet werden, auch zum Speichern der 3DNow!-Registerzustände verwendet werden können. Somit sind keine besonderen Änderungen an Betriebssystemen erforderlich, die diese sonst nicht kennen würden. ⓘ

SSE und AVX

1999 führte Intel den Befehlssatz Streaming SIMD Extensions (SSE) ein, der im Jahr 2000 mit SSE2 folgte. Der erste Zusatz ermöglichte die Auslagerung grundlegender Gleitkommaoperationen vom x87-Stapel, der zweite machte MMX fast überflüssig und ermöglichte es, dass die Befehle von konventionellen Compilern realistisch anvisiert werden konnten. SSE3 wurde 2004 zusammen mit der Prescott-Revision des Pentium-4-Prozessors eingeführt und fügte spezielle Speicher- und Thread-Handling-Befehle hinzu, um die Leistung der HyperThreading-Technologie von Intel zu steigern. AMD lizenzierte den SSE3-Befehlssatz und implementierte die meisten SSE3-Befehle für seine Athlon 64-Prozessoren der Revision E und später. Der Athlon 64 unterstützt HyperThreading nicht und verfügt nicht über die SSE3-Befehle, die nur für HyperThreading verwendet werden. ⓘ

SSE verwarf alle alten Verbindungen zum FPU-Stack. Dies bedeutete auch, dass dieser Befehlssatz alle alten Verbindungen zu früheren Generationen von SIMD-Befehlssätzen wie MMX verwarf. Dies gab den Entwicklern jedoch mehr Freiraum, so dass sie größere Register verwenden konnten, die nicht durch die Größe der FPU-Register begrenzt waren. Die Entwickler schufen acht 128-Bit-Register mit den Bezeichnungen XMM0 bis XMM7 (Anmerkung: In AMD64 wurde die Anzahl der SSE-XMM-Register von 8 auf 16 erhöht). Der Nachteil war jedoch, dass die Betriebssysteme diesen neuen Satz von Anweisungen kennen mussten, um ihre Registerzustände speichern zu können. Daher hat Intel eine leicht modifizierte Version des geschützten Modus entwickelt, den so genannten erweiterten Modus, der die Verwendung von SSE-Befehlen ermöglicht, während sie im normalen geschützten Modus deaktiviert bleiben. Ein Betriebssystem, das SSE kennt, aktiviert den Enhanced Mode, während ein Betriebssystem, das SSE nicht kennt, nur in den traditionellen Protected Mode wechselt. ⓘ

SSE ist ein SIMD-Befehlssatz, der wie 3DNow! nur mit Gleitkommawerten arbeitet. Im Gegensatz zu 3DNow! kappt er jedoch alle Legacy-Verbindungen zum FPU-Stack. Da er über größere Register als 3DNow! verfügt, kann SSE die doppelte Anzahl von Gleitkommazahlen in seinen Registern unterbringen. Der ursprüngliche SSE war, wie 3DNow!, auf einfach genaue Zahlen beschränkt. Mit SSE2 wurde die Fähigkeit eingeführt, auch doppelt genaue Zahlen zu packen, was 3DNow! nicht möglich war, da eine doppelt genaue Zahl 64 Bit groß ist, was der vollen Größe eines einzelnen 3DNow! MMn-Registers wäre. Mit 128 Bit können die SSE XMMn-Register zwei doppelt genaue Gleitkommazahlen in ein Register packen. Daher ist SSE2 für wissenschaftliche Berechnungen viel besser geeignet als SSE1 oder 3DNow!, die auf einfache Genauigkeit beschränkt waren. SSE3 führt keine zusätzlichen Register ein. ⓘ

Die Advanced Vector Extensions (AVX) verdoppelten die Größe der SSE-Register auf 256-Bit-YMM-Register. Außerdem wurde das VEX-Kodierungsschema eingeführt, um die größeren Register unterzubringen, sowie einige Anweisungen zum Permutieren von Elementen. AVX2 führte keine zusätzlichen Register ein, sondern zeichnete sich durch zusätzliche Maskierungs-, Gathering- und Shuffle-Anweisungen aus. ⓘ

AVX-512 bietet eine weitere Erweiterung auf 32 512-Bit-ZMM-Register und ein neues EVEX-Schema. Im Gegensatz zu seinen Vorgängern mit einer monolithischen Erweiterung ist es in viele Untergruppen unterteilt, die von bestimmten CPU-Modellen implementiert werden können. ⓘ

Physikalische Adresserweiterung (PAE)

Die Physical Address Extension (PAE) wurde erstmals beim Intel Pentium Pro und später von AMD bei den Athlon-Prozessoren eingeführt, um die Adressierung von bis zu 64 GB RAM zu ermöglichen. Ohne PAE ist der physische Arbeitsspeicher im geschützten 32-Bit-Modus normalerweise auf 4 GB begrenzt. PAE definiert eine andere Seitentabellenstruktur mit breiteren Seitentabelleneinträgen und einer dritten Ebene der Seitentabelle, die zusätzliche Bits für die physikalische Adresse erlaubt. Obwohl die ersten Implementierungen auf 32-Bit-Prozessoren theoretisch bis zu 64 GB Arbeitsspeicher unterstützten, schränkten Chipsatz- und andere Plattformbeschränkungen oft die tatsächlich nutzbare Größe ein. x86-64-Prozessoren definieren Seitentabellenstrukturen, die theoretisch bis zu 52 Bit physikalische Adresse erlauben, obwohl auch hier Chipsatz- und andere Plattformprobleme (wie die Anzahl der verfügbaren DIMM-Steckplätze und der maximal mögliche Arbeitsspeicher pro DIMM) verhindern, dass ein so großer physikalischer Adressraum realisiert werden kann. Bei x86-64-Prozessoren muss der PAE-Modus vor dem Wechsel in den langen Modus aktiv sein und während des langen Modus aktiv bleiben, so dass es im langen Modus keinen "Nicht-PAE"-Modus gibt. Der PAE-Modus wirkt sich nicht auf die Breite der linearen oder virtuellen Adressen aus. ⓘ

x86-64

In den 2000er Jahren waren die Grenzen der 32-Bit-x86-Prozessoren bei der Speicheradressierung ein Hindernis für ihren Einsatz in Hochleistungsrechenclustern und leistungsstarken Desktop-Workstations. Der in die Jahre gekommene 32-Bit-x86-Prozessor konkurrierte mit wesentlich fortschrittlicheren 64-Bit-RISC-Architekturen, die viel mehr Speicher adressieren konnten. Intel und das gesamte x86-Ökosystem benötigten die 64-Bit-Speicheradressierung, wenn x86 die Ära der 64-Bit-Computer überleben sollte, da Workstation- und Desktop-Softwareanwendungen bald an die Grenzen der 32-Bit-Speicheradressierung stoßen würden. Intel war jedoch der Meinung, dass es der richtige Zeitpunkt war, einen kühnen Schritt zu wagen und den Übergang zu 64-Bit-Desktop-Computern für eine Abkehr von der x86-Architektur im Allgemeinen zu nutzen - ein Experiment, das letztendlich scheiterte. ⓘ

Im Jahr 2001 versuchte Intel, mit seinem Itanium-Prozessor eine 64-Bit-Architektur ohne x86-Architektur namens IA-64 einzuführen, die zunächst auf den Markt für Hochleistungsrechner abzielte, in der Hoffnung, dass sie schließlich die 32-Bit-x86-Architektur ersetzen würde. Während IA-64 mit x86 inkompatibel war, bot der Itanium-Prozessor zwar Emulationsmöglichkeiten für die Übersetzung von x86-Befehlen in IA-64, doch beeinträchtigte dies die Leistung von x86-Programmen so stark, dass es für die Benutzer selten, wenn überhaupt, von Nutzen war: Programmierer mussten x86-Programme für die IA-64-Architektur umschreiben, da ihre Leistung auf Itanium um Größenordnungen schlechter war als auf einem echten x86-Prozessor. Der Markt lehnte den Itanium-Prozessor ab, da er die Abwärtskompatibilität aufhob, und zog es vor, weiterhin x86-Chips zu verwenden, und nur sehr wenige Programme wurden für IA-64 umgeschrieben. ⓘ

AMD beschloss, einen anderen Weg zur 64-Bit-Speicheradressierung einzuschlagen, um sicherzustellen, dass die Abwärtskompatibilität nicht leidet. Im April 2003 brachte AMD den ersten x86-Prozessor mit 64-Bit-Allzweckregistern auf den Markt, den Opteron, der mit der neuen x86-64-Erweiterung (auch als AMD64 oder x64 bekannt) weit mehr als 4 GB virtuellen Speicher adressieren kann. Die 64-Bit-Erweiterungen der x86-Architektur wurden nur im neu eingeführten Long-Mode aktiviert, so dass 32-Bit- und 16-Bit-Anwendungen und -Betriebssysteme einen AMD64-Prozessor einfach im geschützten oder anderen Modus weiter nutzen konnten, ohne auch nur die geringsten Leistungseinbußen und mit voller Kompatibilität zu den ursprünglichen Anweisungen des 16-Bit-Intel 8086. Der Markt reagierte positiv und nahm die 64-Bit-AMD-Prozessoren sowohl für Hochleistungsanwendungen als auch für Geschäfts- und Heimcomputer an. ⓘ

Da der Markt den inkompatiblen Itanium-Prozessor ablehnte und Microsoft AMD64 unterstützte, musste Intel reagieren und stellte im Juli 2004 seinen eigenen x86-64-Prozessor, den Prescott Pentium 4, vor. Infolgedessen wird der Itanium-Prozessor mit seinem IA-64-Befehlssatz nur noch selten verwendet, und x86 ist in seiner x86-64-Variante immer noch die vorherrschende CPU-Architektur in nicht eingebetteten Computern. ⓘ

Mit x86-64 wurde auch das NX-Bit eingeführt, das einen gewissen Schutz gegen Sicherheitslücken bietet, die durch Pufferüberläufe verursacht werden. ⓘ

Infolge des 64-Bit-Beitrags von AMD zur x86-Abstammung und der anschließenden Akzeptanz durch Intel stellten die 64-Bit-RISC-Architekturen keine Bedrohung mehr für das x86-Ökosystem dar und verschwanden fast vom Workstation-Markt. x86-64 begann, in leistungsstarken Supercomputern (in seinen AMD Opteron- und Intel Xeon-Varianten) eingesetzt zu werden, einem Markt, der zuvor das natürliche Habitat für 64-Bit-RISC-Designs (wie die IBM Power-Mikroprozessoren oder SPARC-Prozessoren) war. Der große Sprung in Richtung 64-Bit-Computing und die Beibehaltung der Abwärtskompatibilität mit 32-Bit- und 16-Bit-Software haben die x86-Architektur zu einer äußerst flexiblen Plattform gemacht. x86-Chips werden von kleinen Systemen mit geringem Stromverbrauch (z. B. Intel Quark und Intel Atom) bis hin zu schnellen Gaming-Desktop-Computern (z. B. Intel Core i7 und AMD FX/Ryzen) eingesetzt und dominieren sogar große Supercomputing-Cluster, so dass nur noch die ARM 32-Bit- und 64-Bit-RISC-Architektur als Konkurrent auf dem Smartphone- und Tablet-Markt übrig bleibt. ⓘ

Die x86-Architektur verwendet einen CISC-Befehlssatz mit variabler Instruktionslänge. Speicherzugriffe in Wortgröße sind auch auf nicht Wort-ausgerichtete Speicheradressen erlaubt. Wörter werden in Little-Endian-Richtung gespeichert. Leichte Portierbarkeit von Intel-8085-Assemblercode war eine treibende Kraft der Architekturentwicklung. Dies bedingte einige nicht optimale und im Nachhinein problematische Designentscheidungen. ⓘ

Heutige x86-Prozessoren sind hybride CISC/RISC-Prozessoren, denn sie übersetzen den x86-Befehlssatz zunächst in RISC-Mikro-Instruktionen konstanter Länge, auf die moderne mikro-architektonische Optimierungen angewendet werden können. Die Übergabe erfolgt zunächst an sogenannte Reservierungsstationen, das heißt an kleine Puffer, die den verschiedenen Rechenwerken vorgeschaltet sind. Der erste hybride x86-Prozessor war der Pentium Pro. ⓘ

Virtualisierung

Vor 2005 waren Prozessoren der x86-Architektur nicht in der Lage, die Popek- und Goldberg-Anforderungen zu erfüllen - eine Spezifikation für Virtualisierung, die 1974 von Gerald J. Popek und Robert P. Goldberg entwickelt wurde. Es wurden jedoch sowohl proprietäre als auch quelloffene x86-Virtualisierungshypervisor-Produkte entwickelt, die softwarebasierte Virtualisierung verwenden. Zu den proprietären Systemen gehören Hyper-V, Parallels Workstation, VMware ESX, VMware Workstation, VMware Workstation Player und Windows Virtual PC, während zu den freien und Open-Source-Systemen QEMU, Kernel-based Virtual Machine, VirtualBox und Xen gehören. ⓘ

Die Einführung der AMD-V- und Intel VT-x-Befehlssätze im Jahr 2005 ermöglichte es x86-Prozessoren, die Popek- und Goldberg-Virtualisierungsanforderungen zu erfüllen. ⓘ

Protected und Enhanced Mode

Register

- AX/EAX/RAX: Akkumulator

- BX/EBX/RBX: Basis

- CX/ECX/RCX: Zähler

- DX/EDX/RDX: Daten/Allzweck

- SI/ESI/RSI: Quellindex (Zeichenketten)

- DI/EDI/RDI: Zielindex (Zeichenketten)

- SP/ESP/RSP: Stapelzeiger

- BP/EBP/RBP: Stapelsegment (Anfangsadresse)

- IP/EIP/RIP: Befehlszeiger ⓘ

Virtualisierung

Obwohl die Virtualisierung eines x86-Prozessors aufgrund der umfassenden Architektur aufwendig ist, gibt es mehrere Produkte, die einen virtuellen x86-Prozessor zur Verfügung stellen, darunter VMware und Hyper-V oder auch Open-Source-Software wie Xen oder VirtualBox. Hardwareseitige Virtualisierung gibt es auch als Erweiterung, sie wird bei Intel „Intel VT“ (für Virtualization Technology), bei AMD „AMD Virtualization“ genannt. ⓘ