Metall-Oxid-Halbleiter-Feldeffekttransistor

Ein Metall-Oxid-Halbleiter-Feldeffekttransistor (englisch metal-oxide-semiconductor field-effect transistor, MOSFET, auch MOS-FET, selten MOST) ist eine Bauform eines Transistors, d. h. eine Art elektronisches Ventil. In der Familie der Feldeffekttransistoren zeichnen sich MOSFETs durch ein isoliertes Gate (der Kontakt, mit dem das „Ventil“ angesteuert wird) aus einem Oxid aus und gehören damit zu den Feldeffekttransistoren mit isoliertem Gate (IGFET) bzw. Metall-Isolator-Halbleiter-Feldeffekttransistoren (MISFET). ⓘ

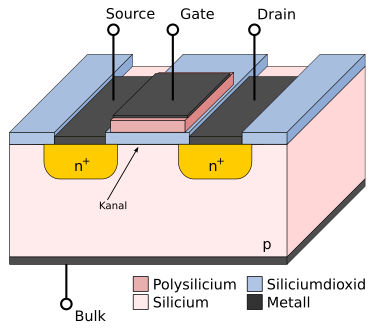

MOSFETs basieren auf einer Metall-Isolator-Halbleiter-Struktur, d. h. einem schichtweisen Aufbaus aus einer isolierten metallischen Gate-Elektrode, einem Halbleiter und dem dazwischen befindlichen oxidischen Dielektrikum (also einem Isolierstoff). In modernen integrierten Schaltung wurde im Laufe der technischen Entwicklung das metallische Gate durch hochdotiertes Polysilizium mit metallähnlichen elektrischen Eigenschaften ersetzt. Trotz des abweichenden Aufbaus wurde auch für diese Variante die Bezeichnung MOSFET weitgehend beibehalten, siehe auch Abschnitt Name. ⓘ

Wie bei allen Feldeffekttransistoren erfolgt die Steuerung des Stromflusses im Halbleiterbereich zwischen den beiden elektrischen Anschlüssen Drain und Source über eine elektrische Steuerspannung (Gate-Source-Spannung) bzw. Steuerpotential (Gate-Potential), vgl. Abschnitt Aufbau und Funktionsweise. Daher sind MOSFETs spannungsgesteuerte aktive elektrische Bauelemente und funktionieren grundlegend anders als bipolare Transistoren, einer anderen bedeutenden Gruppe von Transistoren die stromgesteuert arbeiten, d. h., umso mehr elektrischer Strom durchlassen, je mehr Strom in die Steuerelektrode fließt. ⓘ

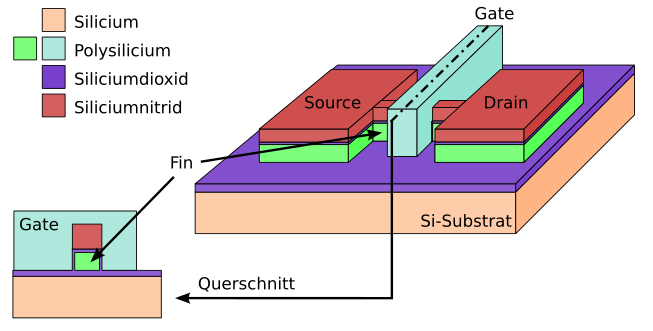

Aufgrund fertigungstechnischer Vorteile ggü. anderen Varianten sind MOSFETs mit Silizium als Halbleitermaterial seit den 1970er Jahren zum meistverwendeten Transistortyp für analoge und digitale integrierte Schaltungen geworden. Hier kommen sie unter anderem als Teil von Logik-Gattern in digitalen Schaltungen zum Einsatz. Die Entwicklung in diesem Bereich ist für die stetige Skalierung der Transistoren bekannt. Hier konnten die Packungsdichte für diese Art von Transistoren um Größenordnungen erhöht und durch Massenfertigung die Herstellungskosten gering gehalten werden, so dass beispielsweise im Jahr 2008 in einem einzelnen Prozessor bis zu 1,9 Milliarden Transistoren verbaut wurden. Durch Nutzung neuer Varianten, wie den FinFETs, konnte die Skalierung weiter fortgesetzt werden. So ist es in 7-nm-Technik möglich, über 54 Milliarden Transistoren in einem Prozessor (Nvidia GA100 Ampere) zu verbauen. ⓘ

Auch bei anderen Anwendungen, wie Schalten von hohen Strömen oder mit hohen Spannungen (vgl. Leistungstransistor) sind Silizium-MOSFETs in vielen Bereichen vertreten oder gar Standard, andere Materialien sind Galliumarsenid oder auch organische Halbleiter. Zunehmend werden jedoch die physikalischen Grenzen von Silizium ausgereizt, und für besondere Anwendungen sind heute andere Halbleitermaterialien mit für diese Anwendung besseren Eigenschaften als Silizium interessant, wie Verbindungshalbleiter oder Halbleiter mit größeren Bandlücken, wie Siliziumcarbid (SiC) und Galliumnitrid (GaN), auch wenn die Fertigungskosten derzeit noch beträchtlich höher liegen. ⓘ

Das Grundprinzip des Feldeffekttransistors wurde erstmals 1925 von Julius Edgar Lilienfeld patentiert. ⓘ

Der Hauptvorteil eines MOSFET besteht darin, dass er im Vergleich zu bipolaren Transistoren (Bipolar Junction Transistors/BJTs) fast keinen Eingangsstrom zur Steuerung des Laststroms benötigt. Bei einem MOSFET im Anreicherungsmodus erhöht eine an den Gate-Anschluss angelegte Spannung die Leitfähigkeit des Bauelements. Bei Transistoren im Verarmungsmodus wird die Leitfähigkeit durch eine an den Gate-Anschluss angelegte Spannung verringert. ⓘ

Das "Metall" in der Bezeichnung MOSFET ist manchmal eine falsche Bezeichnung, da das Gate-Material eine Schicht aus Polysilizium (polykristallines Silizium) sein kann. Auch das "Oxid" in der Bezeichnung kann falsch sein, da verschiedene dielektrische Materialien verwendet werden, um starke Kanäle mit kleineren angelegten Spannungen zu erhalten. ⓘ

Geschichte

Das Grundprinzip dieser Art von Transistor wurde erstmals 1925 von Julius Edgar Lilienfeld patentiert. ⓘ

Die Struktur, die dem MOS-Transistor ähnelt, wurde von den Bell-Wissenschaftlern William Shockley, John Bardeen und Walter Houser Brattain während ihrer Untersuchungen vorgeschlagen, die zur Entdeckung des Transistoreffekts führten. Die Struktur zeigte jedoch nicht die erwarteten Effekte, was an dem Problem des Oberflächenzustands lag: Fallen auf der Halbleiteroberfläche, die die Elektronen unbeweglich halten. 1955 legten Carl Frosch und L. Derick versehentlich eine Schicht aus Siliziumdioxid auf den Siliziumwafer. Weitere Forschungen zeigten, dass Siliziumdioxid die Diffusion von Dotierstoffen in die Siliziumscheibe verhindern konnte. Darauf aufbauend stellte Mohamed M. Atalla fest, dass Siliziumdioxid das Problem einer wichtigen Klasse von Oberflächenzuständen sehr effektiv lösen kann. ⓘ

Daraufhin demonstrierten Atalla und Dawon Kahng ein Bauelement, das die Struktur eines modernen MOS-Transistors aufweist. Die Prinzipien, nach denen dieses Bauelement funktionierte, waren die gleichen wie die, die Bardeen, Shockley und Brattain bei ihrem erfolglosen Versuch, ein Oberflächen-Feldeffekt-Bauelement zu bauen, angewendet hatten. ⓘ

Das Funktionsprinzip von MOSFETs ist etwa 20 Jahre älter als das des Bipolartransistors. Die ersten Patentanmeldungen stammen aus den Jahren 1926 von Julius Edgar Lilienfeld und 1934 von Oskar Heil. Die ersten MOSFETs wurden allerdings erst 1960 von Mohamed M. Atalla und Dawon Kahng in den Bell Labs gefertigt, die mit dem Materialsystem Silizium/Siliziumdioxid einen Fertigungsprozess entwickelten, mit dem sich eine reproduzierbar gute Halbleiter-Isolator-Grenzfläche herstellen ließ. Damit verbunden war die Abkehr vom Germanium als Basismaterial und steigende Anforderungen an die Fertigungsbedingungen (Reinräume, strenges Temperaturregime). ⓘ

Ab Anfang bzw. Mitte 1970 kam dotiertes Polysilizium als Gate-Material zum Einsatz und verdrängte damit aufgedampftes Aluminium. Seit der Jahrtausendwende wurde verstärkt an der neuartigen High-k+Metal-Gate-Technik geforscht und diese 2007 erstmals in der Massenproduktion eingesetzt. ⓘ

Zusammensetzung

In der Regel ist der Halbleiter der Wahl Silizium. In jüngster Zeit haben einige Chip-Hersteller, vor allem IBM und Intel, begonnen, eine chemische Verbindung aus Silizium und Germanium (SiGe) in MOSFET-Kanälen zu verwenden. Leider bilden viele Halbleiter mit besseren elektrischen Eigenschaften als Silizium, wie z. B. Galliumarsenid, keine guten Halbleiter-Isolator-Grenzflächen und sind daher für MOSFETs nicht geeignet. Die Forschung wird fortgesetzt, um Isolatoren mit akzeptablen elektrischen Eigenschaften auf anderen Halbleitermaterialien zu schaffen. ⓘ

Um den Anstieg des Stromverbrauchs aufgrund von Leckströmen im Gate zu vermeiden, wird anstelle von Siliziumdioxid ein hoch-κ-Dielektrikum als Gate-Isolator verwendet, während Polysilizium durch Metallgates ersetzt wird (z. B. Intel, 2009). ⓘ

Das Gate ist vom Kanal durch eine dünne Isolierschicht getrennt, die traditionell aus Siliziumdioxid und später aus Siliziumoxynitrid besteht. Einige Unternehmen haben damit begonnen, im 45-Nanometer-Knoten eine Kombination aus Hoch-κ-Dielektrikum und Metall-Gate einzuführen. ⓘ

Wird eine Spannung zwischen dem Gate- und dem Body-Anschluss angelegt, durchdringt das erzeugte elektrische Feld das Oxid und erzeugt eine Inversionsschicht oder einen Kanal an der Halbleiter-Isolator-Grenzfläche. Die Inversionsschicht bildet einen Kanal, durch den Strom zwischen Source- und Drain-Anschluss fließen kann. Durch Variation der Spannung zwischen Gate und Body wird die Leitfähigkeit dieser Schicht moduliert und damit der Stromfluss zwischen Drain und Source gesteuert. Dies wird als Anreicherungsmodus bezeichnet. ⓘ

Betrieb

Metalloxid-Halbleiter-Struktur

Die traditionelle Metall-Oxid-Halbleiter-Struktur (MOS) wird durch Aufwachsen einer Schicht aus Siliziumdioxid (SiO

2) auf einem Siliziumsubstrat, in der Regel durch thermische Oxidation und Aufbringen einer Metallschicht oder einer Schicht aus polykristallinem Silizium (letzteres wird häufig verwendet). Da das Siliziumdioxid ein dielektrisches Material ist, entspricht seine Struktur einem planaren Kondensator, wobei eine der Elektroden durch einen Halbleiter ersetzt ist. ⓘ

Wenn eine Spannung an eine MOS-Struktur angelegt wird, verändert sie die Ladungsverteilung im Halbleiter. Betrachtet man einen p-Typ-Halbleiter (mit die Dichte der Akzeptoren, p die Dichte der Löcher; p = NA im neutralen Volumen), wird eine positive Spannung, vom Gate zum Body (siehe Abbildung) eine Verarmungsschicht, indem sie die positiv geladenen Löcher von der Gate-Isolator/Halbleiter-Grenzfläche wegdrängt und einen ladungsträgerfreien Bereich mit unbeweglichen, negativ geladenen Akzeptor-Ionen freilässt (siehe Dotierung (Halbleiter)). Wenn hoch genug ist, bildet sich eine hohe Konzentration von negativen Ladungsträgern in einer Inversionsschicht, die sich in einer dünnen Schicht neben der Grenzfläche zwischen dem Halbleiter und dem Isolator befindet. ⓘ

Konventionell wird die Gatespannung, bei der die Volumendichte der Elektronen in der Inversionsschicht gleich der Volumendichte der Löcher im Körper ist, als Schwellenspannung bezeichnet. Wenn die Spannung zwischen Transistor-Gate und Source (VGS) die Schwellenspannung (Vth) übersteigt, wird die Differenz als Übersteuerungsspannung bezeichnet. ⓘ

Diese Struktur mit p-Typ-Körper ist die Grundlage für den n-Typ-MOSFET, der zusätzlich n-Typ-Source- und Drain-Bereiche benötigt. ⓘ

MOS-Kondensatoren und Banddiagramme

Die MOS-Kondensatorstruktur ist das Herzstück des MOSFETs. Betrachten wir einen MOS-Kondensator, bei dem die Siliziumbasis vom p-Typ ist. Wird am Gate eine positive Spannung angelegt, werden Löcher, die sich an der Oberfläche des p-Typ-Substrats befinden, von dem durch die angelegte Spannung erzeugten elektrischen Feld abgestoßen. Zunächst werden die Löcher einfach abgestoßen, und was auf der Oberfläche zurückbleibt, sind unbewegliche (negative) Atome des Akzeptortyps, wodurch ein Verarmungsgebiet auf der Oberfläche entsteht. Zur Erinnerung: Ein Loch entsteht durch ein Akzeptoratom, z. B. Bor, das ein Elektron weniger hat als Silizium. Man könnte sich nun fragen, wie Löcher abgestoßen werden können, wenn sie doch eigentlich gar nicht existieren? Die Antwort ist, dass in Wirklichkeit kein Loch abgestoßen wird, sondern Elektronen durch das positive Feld angezogen werden und diese Löcher füllen, wodurch ein Verarmungsgebiet entsteht, in dem es keine Ladungsträger gibt, da das Elektron nun auf dem Atom fixiert und unbeweglich ist. ⓘ

Mit zunehmender Spannung am Gate gibt es einen Punkt, an dem die Oberfläche oberhalb des Verarmungsbereichs vom p-Typ in den n-Typ umgewandelt wird, da Elektronen aus dem Bulk-Bereich von dem größeren elektrischen Feld angezogen werden. Dies wird als Inversion bezeichnet. Die Schwellenspannung, bei der diese Umwandlung stattfindet, ist einer der wichtigsten Parameter in einem MOSFET. ⓘ

Im Falle eines p-Typ-Volumens findet eine Inversion statt, wenn das intrinsische Energieniveau an der Oberfläche kleiner wird als das Fermi-Niveau an der Oberfläche. Dies kann man aus einem Banddiagramm ersehen. Denken Sie daran, dass das Fermi-Niveau den Typ des betreffenden Halbleiters definiert. Ist das Fermi-Niveau gleich dem Intrinsic-Niveau, so ist der Halbleiter vom intrinsischen oder reinen Typ. Liegt das Fermi-Niveau näher am Leitungsband (Valenzband), so ist der Halbleitertyp vom n-Typ (p-Typ). Wenn also die Gate-Spannung im positiven Sinne erhöht wird (für das gegebene Beispiel), "krümmt" dies das intrinsische Energieniveau-Band, so dass es sich nach unten in Richtung Valenzband wölbt. Wenn das Fermi-Niveau näher am Valenzband liegt (beim p-Typ), gibt es einen Punkt, an dem das Intrinsic-Niveau beginnt, das Fermi-Niveau zu kreuzen, und wenn die Spannung die Schwellenspannung erreicht, kreuzt das Intrinsic-Niveau tatsächlich das Fermi-Niveau, was als Inversion bezeichnet wird. An diesem Punkt wird die Oberfläche des Halbleiters vom p-Typ in den n-Typ invertiert. Wenn das Fermi-Niveau über dem Intrinsic-Niveau liegt, ist der Halbleiter vom n-Typ. Wenn also bei der Inversion das Intrinsic-Niveau das Fermi-Niveau (das näher am Valenzband liegt) erreicht und kreuzt, ändert sich der Halbleitertyp an der Oberfläche entsprechend der relativen Position des Fermi- und des Intrinsic-Energieniveaus. ⓘ

Struktur und Kanalbildung

Ein MOSFET basiert auf der Modulation der Ladungskonzentration durch eine MOS-Kapazität zwischen einer Körperelektrode und einer Gate-Elektrode, die sich oberhalb des Körpers befindet und durch eine dielektrische Gate-Schicht von allen anderen Bauelementbereichen isoliert ist. Wenn ein anderes Dielektrikum als ein Oxid verwendet wird, kann das Bauelement als Metall-Isolator-Halbleiter-FET (MISFET) bezeichnet werden. Im Vergleich zum MOS-Kondensator enthält der MOSFET zwei zusätzliche Anschlüsse (Source und Drain), die jeweils mit einzelnen hochdotierten Bereichen verbunden sind, die durch den Body-Bereich getrennt sind. Diese Bereiche können entweder vom p- oder vom n-Typ sein, müssen aber beide vom gleichen Typ und vom entgegengesetzten Typ zum Body-Bereich sein. Source und Drain sind (im Gegensatz zum Body) hochdotiert, was durch ein "+"-Zeichen hinter der Art der Dotierung angezeigt wird. ⓘ

Handelt es sich bei dem MOSFET um einen n-Kanal- oder nMOS-FET, dann sind Source und Drain n+-Bereiche und der Body ist ein p-Bereich. Handelt es sich bei dem MOSFET um einen p-Kanal- oder pMOS-FET, dann sind Source und Drain p+-Bereiche und der Körper ein n-Bereich. Die Source wird so genannt, weil sie die Quelle der Ladungsträger (Elektronen für n-Kanal, Löcher für p-Kanal) ist, die durch den Kanal fließen; ebenso ist der Drain der Ort, an dem die Ladungsträger den Kanal verlassen. ⓘ

Die Belegung der Energiebänder in einem Halbleiter wird durch die Position des Fermi-Niveaus relativ zu den Energiebandkanten des Halbleiters bestimmt. ⓘ

Bei ausreichender Gatespannung wird die Valenzbandkante weit vom Fermi-Niveau entfernt, und Löcher aus dem Körper werden vom Gate weggetrieben. ⓘ

Bei noch größerer Gatespannung wird die Leitungsbandkante in der Nähe der Halbleiteroberfläche in die Nähe des Fermi-Niveaus gebracht, wodurch die Oberfläche mit Elektronen in einer Inversionsschicht oder einem n-Kanal an der Grenzfläche zwischen dem p-Gebiet und dem Oxid besiedelt wird. Dieser Leitungskanal erstreckt sich zwischen der Source und der Drain, und wenn eine Spannung zwischen den beiden Elektroden angelegt wird, fließt Strom durch ihn. Eine Erhöhung der Spannung am Gate führt zu einer höheren Elektronendichte in der Inversionsschicht und erhöht somit den Stromfluss zwischen Source und Drain. Bei Gate-Spannungen unterhalb des Schwellenwerts ist der Kanal nur schwach besetzt, und zwischen Source und Drain kann nur ein sehr geringer Unterschwellen-Leckstrom fließen. ⓘ

Wenn eine negative Gate-Source-Spannung (positive Source-Gate-Spannung) angelegt wird, entsteht an der Oberfläche des n-Bereichs ein p-Kanal, analog zum n-Kanal, jedoch mit entgegengesetzten Polaritäten der Ladungen und Spannungen. Wenn zwischen Gate und Source eine Spannung angelegt wird, die kleiner ist als der Schwellenwert (eine negative Spannung für den p-Kanal), verschwindet der Kanal, und zwischen Source und Drain kann nur ein sehr geringer Unterschwellenstrom fließen. Das Bauelement kann aus einem Silizium-auf-Isolator-Bauelement bestehen, bei dem ein vergrabenes Oxid unter einer dünnen Halbleiterschicht gebildet wird. Wenn der Kanalbereich zwischen dem Gate-Dielektrikum und dem vergrabenen Oxidbereich sehr dünn ist, wird der Kanal als ultradünner Kanalbereich bezeichnet, wobei die Source- und Drain-Bereiche auf beiden Seiten in oder über der dünnen Halbleiterschicht ausgebildet sind. Es können auch andere Halbleitermaterialien verwendet werden. Wenn die Source- und Drain-Bereiche ganz oder teilweise oberhalb des Kanals ausgebildet sind, spricht man von erhöhten Source-/Drain-Bereichen. ⓘ

| Parameter | nMOSFET | pMOSFET | |

|---|---|---|---|

| Source-/Drain-Typ | n-Typ | p-Typ | |

| Kanal-Typ (MOS-Kondensator) |

n-Typ | p-Typ | |

| Gate Typ |

Polysilizium | n+ | p+ |

| Metall | φm ~ Si-Leitungsband | φm ~ Si- Valenzband | |

| Well-Typ | p-Typ | n-Typ | |

| Schwellenspannung, Vth |

|

| |

| Bandverbiegung | Abwärts | Nach oben | |

| Inversionsschichtträger | Elektronen | Löcher | |

| Art des Substrats | p-Typ | n-Typ | |

Betriebsarten

oben links: Unterschwellenwert, oben rechts: Ohmscher Modus, unten links: Aktiver Modus bei Beginn des Pinch-Offs, unten rechts: Aktiver Modus weit nach dem Pinch-Off - deutliche Modulation der Kanallänge ⓘ

Der Betrieb eines MOSFET kann in drei verschiedene Modi unterteilt werden, die von den Spannungen an den Anschlüssen abhängen. In der folgenden Diskussion wird ein vereinfachtes algebraisches Modell verwendet. Die Eigenschaften moderner MOSFETs sind komplexer als das hier vorgestellte algebraische Modell. ⓘ

Bei einem n-Kanal-MOSFET im Anreicherungsmodus sind die drei Betriebsarten:

- Cutoff-, Subthreshold- und Schwachinversionsmodus ⓘ

Wenn VGS < Vth: wobei die Gate-Source-Vorspannung und die Schwellenspannung des Bauelements ist. ⓘ

Nach dem grundlegenden Schwellenwertmodell ist der Transistor ausgeschaltet, und es findet keine Leitung zwischen Drain und Source statt. Ein genaueres Modell berücksichtigt die Auswirkungen der thermischen Energie auf die Fermi-Dirac-Verteilung der Elektronenenergien, die es einigen der energiereicheren Elektronen an der Source ermöglichen, in den Kanal einzutreten und zum Drain zu fließen. Dies führt zu einem Unterschwellenstrom, der eine Exponentialfunktion der Gate-Source-Spannung ist. Während der Strom zwischen Drain und Source im Idealfall gleich Null sein sollte, wenn der Transistor als ausgeschalteter Schalter verwendet wird, gibt es einen Strom bei schwacher Inversion, der manchmal auch als Leckstrom im Unterschwellenbereich bezeichnet wird. ⓘ

Bei schwacher Inversion, bei der die Source mit der Masse verbunden ist, variiert der Strom exponentiell mit wie ungefähr durch gegeben ist:

wobei = Strom bei die Thermospannung und der Steigungsfaktor n ist gegeben durch:

mit = Kapazität der Verarmungsschicht und = Kapazität der Oxidschicht. Diese Gleichung wird im Allgemeinen verwendet, ist aber nur eine adäquate Annäherung für die an das Substrat gebundene Source. Für die Source, die nicht mit dem Substrat verbunden ist, lautet die Gleichung für den Drainstrom in der Sättigung im Unterschwellenbereich ⓘ

wobei der der Kanaltrenner ist, der gegeben ist durch:

mit = Kapazität der Verarmungsschicht und = Kapazität der Oxidschicht. In einem Bauelement mit langem Kanal gibt es keine Drain-Spannungsabhängigkeit des Stroms, wenn Wenn sich jedoch die Kanallänge verringert, führt die durch den Drain verursachte Absenkung der Barriere zu einer Drain-Spannungsabhängigkeit, die auf komplexe Weise von der Geometrie des Bauelements abhängt (z. B. Dotierung des Kanals, Dotierung der Sperrschicht usw.). Häufig wird die Schwellenspannung Vth für diese Betriebsart als die Gatespannung definiert, bei der ein ausgewählter Wert des Stroms ID0 auftritt, z. B. ID0 = 1 μA, was nicht unbedingt der gleiche Vth-Wert ist, der in den Gleichungen für die folgenden Betriebsarten verwendet wird. ⓘ

Einige analoge Mikropower-Schaltungen sind so konzipiert, dass sie die Vorteile der Unterschwellenleitung nutzen. Da die MOSFETs in diesen Schaltungen im Schwachinversionsbereich arbeiten, liefern sie das höchstmögliche Verhältnis von Transkonduktanz zu Strom, nämlich: Es entspricht fast dem eines bipolaren Transistors. ⓘ

Die I-U-Kurve unter dem Schwellenwert hängt exponentiell von der Schwellenspannung ab, was zu einer starken Abhängigkeit von Fertigungsvariationen führt, die sich auf die Schwellenspannung auswirken, z. B. Variationen der Oxiddicke, der Sperrschichttiefe oder der Body-Dotierung, die den Grad der durch Drain verursachten Barrieresenkung verändern. Die daraus resultierende Empfindlichkeit gegenüber Fertigungsschwankungen erschwert die Optimierung von Leckstrom und Leistung. ⓘ

- Triodenmodus oder linearer Bereich (auch als ohmscher Modus bezeichnet) ⓘ

Wenn VGS > Vth und VDS < VGS - Vth: Der Transistor ist eingeschaltet, und es ist ein Kanal entstanden, der einen Stromfluss zwischen Drain und Source ermöglicht. Der MOSFET arbeitet wie ein Widerstand, der durch die Gate-Spannung im Verhältnis zur Source- und Drain-Spannung gesteuert wird. Der Strom vom Drain zur Source wird wie folgt modelliert:

wobei ist die effektive Ladungsträgermobilität, ist die Gate-Breite, ist die Gate-Länge und ist die Gate-Oxid-Kapazität pro Flächeneinheit. Der Übergang vom exponentiellen Unterschwellenbereich zum Triodenbereich ist nicht so scharf, wie die Gleichungen vermuten lassen. ⓘ

- Sättigung oder aktiver Modus ⓘ

Wenn VGS > Vth und VDS ≥ (VGS - Vth): Der Schalter ist eingeschaltet, und es ist ein Kanal entstanden, der einen Stromfluss zwischen Drain und Source ermöglicht. Da die Drain-Spannung höher ist als die Source-Spannung, breiten sich die Elektronen aus, und die Leitung erfolgt nicht durch einen engen Kanal, sondern durch eine breitere, zwei- oder dreidimensionale Stromverteilung, die sich von der Grenzfläche weg und tiefer in das Substrat hinein erstreckt. Der Beginn dieses Bereichs wird auch als Pinch-off bezeichnet, um das Fehlen eines Kanalbereichs in der Nähe des Drains anzuzeigen. Obwohl sich der Kanal nicht über die gesamte Länge des Bauelements erstreckt, ist das elektrische Feld zwischen dem Drain und dem Kanal sehr hoch, und die Leitung wird fortgesetzt. Der Drain-Strom ist nun nur noch schwach von der Drain-Spannung abhängig und wird in erster Linie von der Gate-Source-Spannung gesteuert:

Der zusätzliche Faktor λ, der Parameter für die Modulation der Kanallänge, modelliert die Abhängigkeit des Stroms von der Drain-Spannung aufgrund des Early-Effekts oder der Modulation der Kanallänge. Nach dieser Gleichung, einem wichtigen Entwurfsparameter, ist die MOSFET-Transkonduktanz:

wobei die Kombination Vov = VGS - Vth als Übersteuerungsspannung bezeichnet wird, und wobei VDSsat = VGS - Vth eine kleine Diskontinuität in berücksichtigt, die sonst am Übergang zwischen Trioden- und Sättigungsbereich auftreten würde. ⓘ

Ein weiterer wichtiger Entwurfsparameter ist der MOSFET-Ausgangswiderstand rout, der sich wie folgt ergibt:

- . ⓘ

rout ist der Kehrwert von gDS, wobei . ID der Ausdruck im Sättigungsbereich ist. ⓘ

Wird λ mit Null angesetzt, ergibt sich ein unendlicher Ausgangswiderstand des Bauelements, der zu unrealistischen Schaltungsvorhersagen führt, insbesondere bei analogen Schaltungen. ⓘ

Wenn die Kanallänge sehr kurz wird, werden diese Gleichungen ziemlich ungenau. Es treten neue physikalische Effekte auf. Beispielsweise kann der Ladungsträgertransport im aktiven Modus durch Geschwindigkeitssättigung begrenzt werden. Wenn die Geschwindigkeitssättigung dominiert, ist der Sättigungsdrainstrom eher linear als quadratisch in VGS. Bei noch kürzeren Längen transportieren die Ladungsträger mit einer Streuung von nahezu Null, was als quasi-ballistischer Transport bezeichnet wird. Im ballistischen Regime bewegen sich die Ladungsträger mit einer Injektionsgeschwindigkeit, die die Sättigungsgeschwindigkeit übersteigen kann und sich bei hoher Inversionsladungsdichte der Fermi-Geschwindigkeit nähert. Darüber hinaus erhöht die durch das Drain induzierte Absenkung der Barriere den Ausschaltstrom und erfordert zum Ausgleich eine Erhöhung der Schwellenspannung, was wiederum den Sättigungsstrom verringert. ⓘ

Body-Effekt

Die Belegung der Energiebänder in einem Halbleiter wird durch die Position des Fermi-Niveaus relativ zu den Energiebandkanten des Halbleiters bestimmt. Die Anwendung einer Sperrvorspannung zwischen Source und Substrat am Source-Body-Pn-Übergang führt zu einer Aufspaltung zwischen den Fermi-Niveaus für Elektronen und Löcher, wodurch das Fermi-Niveau für den Kanal weiter von der Bandkante entfernt wird, was die Belegung des Kanals verringert. Dadurch erhöht sich die zur Herstellung des Kanals erforderliche Gate-Spannung, wie in der Abbildung zu sehen ist. Diese Änderung der Kanalstärke durch Anlegen einer Sperrvorspannung wird als "Body-Effekt" bezeichnet. ⓘ

Vereinfacht ausgedrückt, positioniert die Gate-to-Body-Vorspannung VGB die Leitungsband-Energieniveaus, während die Source-to-Body-Vorspannung VSB das Elektronen-Fermi-Niveau in der Nähe der Grenzfläche positioniert und über die Belegung dieser Niveaus in der Nähe der Grenzfläche und damit über die Stärke der Inversionsschicht oder des Kanals entscheidet. ⓘ

Der Körpereffekt auf den Kanal kann durch eine Modifikation der Schwellenspannung beschrieben werden, die durch die folgende Gleichung angenähert wird:

wobei VTB die Schwellenspannung bei vorhandener Substratvorspannung ist und VT0 der Null-VSB-Wert der Schwellenspannung ist, der Körper-Effekt-Parameter ist und 2φB der ungefähre Potenzialabfall zwischen Oberfläche und Volumen über der Verarmungsschicht ist, wenn VSB = 0 und die Gate-Vorspannung ausreicht, um sicherzustellen, dass ein Kanal vorhanden ist. Wie diese Gleichung zeigt, führt eine Sperrvorspannung VSB > 0 zu einem Anstieg der Schwellenspannung VTB und erfordert daher eine größere Gate-Spannung, bevor sich der Kanal füllt. ⓘ

Der Body kann als zweites Gate betrieben werden und wird manchmal als "Back-Gate" bezeichnet; der Body-Effekt wird manchmal auch als "Back-Gate-Effekt" bezeichnet. ⓘ

Schaltkreissymbole

Für den MOSFET wird eine Vielzahl von Symbolen verwendet. Die Grundform ist im Allgemeinen eine Linie für den Kanal, von der Source und Drain im rechten Winkel abgehen und dann im rechten Winkel in dieselbe Richtung wie der Kanal zurückbiegen. Manchmal werden drei Liniensegmente für den Anreicherungsmodus und eine durchgezogene Linie für den Verarmungsmodus verwendet (siehe Verarmungs- und Anreicherungsmodus). Eine weitere Linie wird parallel zum Kanal für das Gate gezeichnet. ⓘ

Die Bulk- oder Body-Verbindung, falls vorhanden, ist mit der Rückseite des Kanals verbunden, wobei ein Pfeil auf pMOS oder nMOS hinweist. Pfeile zeigen immer von P nach N, so dass bei einem NMOS (N-Kanal in P-Well oder P-Substrat) der Pfeil nach innen zeigt (vom Bulk zum Kanal). Wenn der Bulk mit der Source verbunden ist (wie es bei diskreten Bauelementen in der Regel der Fall ist), ist er manchmal so abgewinkelt, dass er mit der Source, die den Transistor verlässt, zusammenfällt. Wenn der Bulk nicht dargestellt wird (was bei IC-Designs häufig der Fall ist, da sie in der Regel einen gemeinsamen Bulk haben), wird manchmal ein Inversionssymbol verwendet, um PMOS anzuzeigen; alternativ kann ein Pfeil auf der Source in der gleichen Weise wie bei bipolaren Transistoren verwendet werden (out für nMOS, in für pMOS). ⓘ

Vergleich der MOSFET-Symbole für den Anreicherungsmodus und den Verarmungsmodus zusammen mit den JFET-Symbolen. Die Ausrichtung der Symbole (vor allem die Position der Source im Verhältnis zur Drain) ist so, dass positive Spannungen höher auf der Seite erscheinen als weniger positive Spannungen, was bedeutet, dass der Strom auf der Seite "nach unten" fließt:

| P-Kanal |

|

|

|

|

|

|---|---|---|---|---|---|

| N-Kanal |

|

|

|

|

|

| JFET | MOSFET erweitert. | MOSFET erweitert. (kein Volumen) | MOSFET abw. | ||

In Schaltplänen, in denen G, S, D nicht beschriftet sind, geben die detaillierten Merkmale des Symbols an, welcher Anschluss die Source und welcher der Drain ist. Bei MOSFET-Symbolen im Anreicherungs- und Verarmungsmodus (in den Spalten zwei und fünf) ist der Source-Anschluss derjenige, der mit dem Dreieck verbunden ist. Außerdem wird in diesem Diagramm das Gate als "L"-Form dargestellt, dessen Eingangsschenkel näher an S als an D liegt, was ebenfalls auf die beiden Anschlüsse hinweist. Diese Symbole werden jedoch oft mit einem T-förmigen Gatter gezeichnet (wie an anderer Stelle auf dieser Seite), so dass man sich auf das Dreieck verlassen muss, um den Source-Anschluss zu bestimmen. ⓘ

Bei den Symbolen, in denen der Bulk- oder Body-Anschluss dargestellt ist, ist er hier intern mit der Source verbunden (d. h. die schwarzen Dreiecke in den Diagrammen in den Spalten 2 und 5). Dies ist eine typische, aber keineswegs die einzige wichtige Konfiguration. Im Allgemeinen ist der MOSFET ein Bauelement mit vier Anschlüssen, und in integrierten Schaltungen haben viele MOSFETs einen gemeinsamen Körperanschluss, der nicht unbedingt mit den Source-Anschlüssen aller Transistoren verbunden ist. ⓘ

ⓘSchaltzeichen diskreter MOSFETs (Auswahl verschiedener Darstellungsvarianten) Leitungs- /

KanaltypAnreicherungstyp

(selbstsperrend)Verarmungstyp

(selbstleitend)p-Kanal

n-Kanal

Anwendungen

Digitale integrierte Schaltungen wie Mikroprozessoren und Speicherbausteine enthalten Tausende bis Millionen von integrierten MOSFET-Transistoren auf jedem Baustein, die die grundlegenden Schaltfunktionen für die Implementierung von Logikgattern und die Datenspeicherung bereitstellen. Diskrete Bauelemente werden in großem Umfang in Anwendungen wie Schaltnetzteilen, Antrieben mit variabler Frequenz und anderen Anwendungen der Leistungselektronik eingesetzt, bei denen jedes Bauelement Tausende von Watt schalten kann. Radiofrequenzverstärker bis zum UHF-Spektrum verwenden MOSFET-Transistoren als analoge Signal- und Leistungsverstärker. Funksysteme verwenden MOSFETs auch als Oszillatoren oder Mischer, um Frequenzen umzuwandeln. MOSFET-Bauelemente werden auch in Tonfrequenz-Leistungsverstärkern für Beschallungsanlagen, Beschallungsanlagen und Heim- und Auto-Soundsysteme eingesetzt. ⓘ

Integrierte MOS-Schaltungen

Nach der Entwicklung von Reinräumen zur Verringerung der Verschmutzung auf ein zuvor nicht für notwendig erachtetes Niveau sowie der Fotolithografie und des Planarverfahrens, die die Herstellung von Schaltkreisen in nur wenigen Schritten ermöglichen, bot das Si-SiO2-System die technischen Vorteile niedriger Produktionskosten (pro Schaltkreis) und einfacher Integration. Vor allem aufgrund dieser beiden Faktoren wurde der MOSFET zum am häufigsten verwendeten Transistortyp in integrierten Schaltungen. ⓘ

General Microelectronics stellte 1964 den ersten kommerziellen integrierten MOS-Schaltkreis vor. ⓘ

Darüber hinaus bedeutet die als CMOS bezeichnete Methode, zwei komplementäre MOSFETs (P-Kanal und N-Kanal) in einen Hoch/Tief-Schalter zu koppeln, dass digitale Schaltungen sehr wenig Strom verbrauchen, außer wenn sie tatsächlich geschaltet werden. ⓘ

Die ersten Mikroprozessoren ab 1970 waren alle MOS-Mikroprozessoren, d. h. sie wurden vollständig aus PMOS-Logik oder NMOS-Logik hergestellt. In den 1970er Jahren wurden MOS-Mikroprozessoren oft mit CMOS-Mikroprozessoren und bipolaren Bit-Slice-Prozessoren verglichen. ⓘ

CMOS-Schaltungen

Der MOSFET wird in der digitalen komplementären Metall-Oxid-Halbleiter-Logik (CMOS) verwendet, die p- und n-Kanal-MOSFETs als Bausteine einsetzt. Überhitzung ist ein großes Problem bei integrierten Schaltungen, da immer mehr Transistoren in immer kleinere Chips gepackt werden. CMOS-Logik senkt den Stromverbrauch, da (im Idealfall) kein Strom fließt und somit auch kein Strom verbraucht wird, es sei denn, die Eingänge der Logikgatter werden geschaltet. CMOS erreicht diese Stromreduzierung, indem jeder nMOSFET durch einen pMOSFET ergänzt wird und beide Gates und beide Drains miteinander verbunden werden. Eine hohe Spannung an den Gates bewirkt, dass der nMOSFET leitet und der pMOSFET nicht leitet, und eine niedrige Spannung an den Gates bewirkt das Gegenteil. Während der Schaltzeit, wenn die Spannung von einem Zustand in den anderen wechselt, leiten beide MOSFETs kurzzeitig. Diese Anordnung reduziert den Stromverbrauch und die Wärmeentwicklung erheblich. ⓘ

Digital

Das Wachstum digitaler Technologien wie des Mikroprozessors hat die MOSFET-Technologie schneller vorangebracht als jede andere Art von Transistoren auf Siliziumbasis. Ein großer Vorteil von MOSFETs für das digitale Schalten ist, dass die Oxidschicht zwischen Gate und Kanal verhindert, dass Gleichstrom durch das Gate fließt, was den Stromverbrauch weiter senkt und eine sehr hohe Eingangsimpedanz ergibt. Das isolierende Oxid zwischen Gate und Kanal isoliert einen MOSFET in einer Logikstufe effektiv von früheren und späteren Stufen, wodurch ein einziger MOSFET-Ausgang eine beträchtliche Anzahl von MOSFET-Eingängen ansteuern kann. Bipolartransistor-basierte Logik (z. B. TTL) verfügt nicht über eine so hohe Fanout-Kapazität. Diese Isolierung macht es den Entwicklern auch leichter, bis zu einem gewissen Grad Ladeeffekte zwischen den einzelnen Logikstufen zu ignorieren. Dieses Ausmaß wird durch die Betriebsfrequenz bestimmt: Mit steigender Frequenz nimmt die Eingangsimpedanz der MOSFETs ab. ⓘ

Analog

Die Vorteile der MOSFETs in digitalen Schaltungen lassen sich nicht auf alle analogen Schaltungen übertragen. Die beiden Schaltungstypen nutzen unterschiedliche Eigenschaften des Transistorverhaltens aus. Digitale Schaltungen schalten um und verbringen die meiste Zeit damit, entweder ganz ein- oder ganz auszuschalten. Der Übergang vom einen zum anderen ist nur im Hinblick auf die erforderliche Geschwindigkeit und Ladung von Bedeutung. Analoge Schaltungen sind auf den Betrieb im Übergangsbereich angewiesen, wo kleine Änderungen von Vgs den Ausgangsstrom (Drain) modulieren können. JFETs und bipolare Sperrschichttransistoren (BJTs) werden aus Gründen der genauen Anpassung (benachbarter Bauelemente in integrierten Schaltungen), der höheren Transkonduktanz und bestimmter Temperatureigenschaften bevorzugt, die die Vorhersagbarkeit der Leistung bei schwankender Schaltungstemperatur erleichtern. ⓘ

Dennoch werden MOSFETs wegen ihrer Vorteile (kein Gatestrom, hohe und einstellbare Ausgangsimpedanz und verbesserte Robustheit im Vergleich zu BJTs, die schon durch ein leichtes Durchbrechen der Emitter-Basis dauerhaft geschädigt werden können) in vielen Arten von Analogschaltungen eingesetzt. Die Eigenschaften und die Leistung vieler analoger Schaltungen können durch Änderung der Größe (Länge und Breite) der verwendeten MOSFETs nach oben oder unten skaliert werden. Im Vergleich dazu hat bei bipolaren Transistoren die Größe des Bauelements keinen wesentlichen Einfluss auf die Leistung. Die idealen Eigenschaften von MOSFETs in Bezug auf den Gate-Strom (Null) und die Drain-Source-Offset-Spannung (Null) machen sie außerdem zu nahezu idealen Schaltelementen und machen analoge Schaltungen mit geschalteten Kondensatoren praktisch. In ihrem linearen Bereich können MOSFETs als Präzisionswiderstände eingesetzt werden, die einen viel höheren Regelwiderstand als BJTs haben können. In Schaltungen mit hoher Leistung haben MOSFETs manchmal den Vorteil, dass sie nicht wie BJTs unter thermischem Durchgehen leiden. Außerdem können MOSFETs so konfiguriert werden, dass sie als Kondensatoren und Gyratorschaltungen fungieren, wodurch aus ihnen hergestellte Operationsverstärker als Induktoren erscheinen können. Dies bedeutet, dass komplette analoge Schaltungen auf einem Siliziumchip auf viel kleinerem Raum und mit einfacheren Fertigungstechniken hergestellt werden können. MOSFETs sind aufgrund ihrer Toleranz gegenüber induktiven Rückkopplungen ideal zum Schalten induktiver Lasten geeignet. ⓘ

Einige ICs kombinieren analoge und digitale MOSFET-Schaltkreise auf einem einzigen integrierten Mixed-Signal-Schaltkreis, wodurch die benötigte Leiterplattenfläche noch kleiner wird. Dies macht es erforderlich, die analogen Schaltungen von den digitalen Schaltungen auf Chipebene zu isolieren, was zur Verwendung von Isolationsringen und Silizium auf Isolator (SOI) führt. Da MOSFETs für eine bestimmte Leistung mehr Platz benötigen als BJTs, können BJTs und MOSFETs in einem einzigen Bauelement untergebracht werden. Geräte mit gemischten Transistoren werden Bi-FETs (bipolare FETs) genannt, wenn sie nur einen BJT-FET enthalten, und BiCMOS (bipolar-CMOS), wenn sie komplementäre BJT-FETs enthalten. Diese Bauelemente haben die Vorteile isolierter Gates und höherer Stromdichte. ⓘ

Analoge Schalter

MOSFET-Analogschalter verwenden den MOSFET, um analoge Signale weiterzuleiten, wenn er eingeschaltet ist, und als hohe Impedanz, wenn er ausgeschaltet ist. Signale fließen in beide Richtungen über einen MOSFET-Schalter. Bei dieser Anwendung tauschen Drain und Source eines MOSFET je nach den relativen Spannungen der Source/Drain-Elektroden die Plätze. Die Source ist die negativere Seite bei einem N-MOS oder die positivere Seite bei einem P-MOS. Alle diese Schalter sind durch ihre Gate-Source-, Gate-Drain- und Source-Drain-Spannungen hinsichtlich der Signale, die sie durchlassen oder stoppen können, begrenzt; ein Überschreiten der Spannungs-, Strom- oder Leistungsgrenzen führt möglicherweise zu einer Beschädigung des Schalters. ⓘ

Einzeltyp

Dieser analoge Schalter verwendet einen einfachen MOSFET mit vier Anschlüssen, entweder vom Typ P oder N. ⓘ

Bei einem n-Typ-Schalter ist der Body mit der negativsten Versorgungsspannung (normalerweise GND) verbunden, und das Gate wird zur Steuerung des Schalters verwendet. Immer wenn die Gate-Spannung die Source-Spannung um mindestens eine Schwellenspannung übersteigt, wird der MOSFET leitend. Je höher die Spannung ist, desto mehr kann der MOSFET leiten. Ein N-MOS-Schalter lässt alle Spannungen durch, die kleiner sind als Vgate - Vtn. Wenn der Schalter leitet, arbeitet er in der Regel im linearen (oder ohmschen) Betriebsmodus, da die Source- und Drain-Spannungen in der Regel nahezu gleich sind. ⓘ

Bei einem P-MOS ist der Body mit der höchsten positiven Spannung verbunden, und das Gate wird auf ein niedrigeres Potenzial gebracht, um den Schalter einzuschalten. Der P-MOS-Schalter lässt alle Spannungen durch, die höher sind als Vgate - Vtp (die Schwellenspannung Vtp ist im Fall von P-MOS im Anreicherungsmodus negativ). ⓘ

Doppeltyp (CMOS)

Dieser "komplementäre" oder CMOS-Schaltertyp verwendet einen P-MOS- und einen N-MOS-FET, um den Einschränkungen des Single-Type-Schalters entgegenzuwirken. Die Drains und Sources der FETs sind parallel geschaltet, der Körper des P-MOS ist mit dem hohen Potenzial (VDD) und der Körper des N-MOS mit dem niedrigen Potenzial (gnd) verbunden. Um den Schalter einzuschalten, wird das Gate des P-MOS auf das niedrige Potenzial und das Gate des N-MOS auf das hohe Potenzial gelegt. Bei Spannungen zwischen VDD - Vtn und gnd - Vtp leiten beide FETs das Signal; bei Spannungen unter gnd - Vtp leitet der N-MOS allein; und bei Spannungen über VDD - Vtn leitet der P-MOS allein. ⓘ

Die Spannungsgrenzen für diesen Schalter sind die Gate-Source-, Gate-Drain- und Source-Drain-Spannungsgrenzen für beide FETs. Außerdem ist der P-MOS in der Regel zwei- bis dreimal breiter als der N-MOS, so dass der Schalter für die Geschwindigkeit in beiden Richtungen ausgeglichen ist. ⓘ

Tri-State-Schaltungen enthalten manchmal einen CMOSFET-Schalter an ihrem Ausgang, um im eingeschalteten Zustand ein niederohmiges Vollbereichssignal und im ausgeschalteten Zustand ein hochohmiges Mittensignal zu erzeugen. ⓘ

Aufbau

Gate-Material

Das wichtigste Kriterium für das Gate-Material ist, dass es ein guter Leiter ist. Hochdotiertes polykristallines Silizium ist ein akzeptabler, aber sicher kein idealer Leiter und leidet in seiner Rolle als Standard-Gate-Material auch unter einigen eher technischen Mängeln. Dennoch gibt es mehrere Gründe, die für die Verwendung von Polysilizium sprechen:

- Die Schwellenspannung (und damit der Drain-Source-Einschaltstrom) wird durch den Unterschied in der Austrittsarbeit zwischen dem Gate-Material und dem Kanalmaterial beeinflusst. Da es sich bei Polysilizium um einen Halbleiter handelt, kann seine Arbeitsfunktion durch Anpassung der Art und Höhe der Dotierung moduliert werden. Da Polysilizium die gleiche Bandlücke wie der darunter liegende Siliziumkanal hat, ist es außerdem recht einfach, die Arbeitsfunktion so einzustellen, dass niedrige Schwellenspannungen sowohl für NMOS- als auch für PMOS-Bauelemente erreicht werden. Im Gegensatz dazu lassen sich die Arbeitsfunktionen von Metallen nicht so leicht modulieren, so dass die Abstimmung der Arbeitsfunktion zur Erzielung niedriger Schwellenspannungen (LVT) zu einer großen Herausforderung wird. Darüber hinaus erfordert die Erzielung niedriger Schwellenspannungen sowohl bei PMOS- als auch bei NMOS-Bauelementen manchmal die Verwendung unterschiedlicher Metalle für jeden Bauelementetyp. Bimetallische integrierte Schaltungen (d. h. eine Art von Metall für die Gate-Elektroden von NFETS und eine zweite Art von Metall für die Gate-Elektroden von PFETS) sind zwar nicht üblich, aber in der Patentliteratur bekannt und bieten einige Vorteile bei der Abstimmung der elektrischen Gesamtleistung der Schaltungen.

- Die Silizium-SiO2-Grenzfläche ist gut erforscht und weist bekanntlich relativ wenige Defekte auf. Im Gegensatz dazu weisen viele Metall-Isolator-Grenzflächen erhebliche Defekte auf, die zu Fermi-Level-Pinning, Aufladung oder anderen Phänomenen führen können, die letztlich die Leistung der Bauelemente beeinträchtigen.

- Bei der Herstellung von MOSFET-ICs ist es vorzuziehen, das Gate-Material vor bestimmten Hochtemperaturschritten abzuscheiden, um leistungsfähigere Transistoren herzustellen. Solche Hochtemperaturschritte würden einige Metalle schmelzen, was die Arten von Metallen einschränkt, die in einem auf Metallgates basierenden Prozess verwendet werden können. ⓘ

Obwohl Polysilizium-Gates in den letzten zwanzig Jahren der De-facto-Standard waren, haben sie einige Nachteile, die dazu geführt haben, dass sie in Zukunft wahrscheinlich durch Metall-Gates ersetzt werden. Zu diesen Nachteilen gehören:

- Polysilizium ist kein guter Leiter (der Widerstand ist etwa 1000-mal höher als bei Metallen), was die Signalausbreitungsgeschwindigkeit durch das Material verringert. Der Widerstand kann durch Erhöhung der Dotierung gesenkt werden, aber selbst hochdotiertes Polysilizium ist nicht so leitfähig wie die meisten Metalle. Um die Leitfähigkeit weiter zu verbessern, wird manchmal ein Hochtemperaturmetall wie Wolfram, Titan, Kobalt und neuerdings auch Nickel mit den oberen Schichten des Polysiliziums legiert. Ein solches Mischmaterial wird als Silizid bezeichnet. Die Silizid-Polysilizium-Kombination hat bessere elektrische Eigenschaften als Polysilizium allein und schmilzt bei der Weiterverarbeitung trotzdem nicht. Auch die Schwellenspannung ist nicht wesentlich höher als bei Polysilizium allein, weil das Silizidmaterial nicht in der Nähe des Kanals liegt. Das Verfahren, bei dem Silizid sowohl auf der Gate-Elektrode als auch auf den Source- und Drain-Bereichen gebildet wird, wird manchmal auch als Salizid, d. h. selbstausrichtendes Silizid, bezeichnet.

- Wenn die Transistoren extrem verkleinert werden, muss die dielektrische Schicht des Gates sehr dünn sein, etwa 1 nm bei modernen Technologien. Ein hier zu beobachtendes Phänomen ist die so genannte Polyverarmung, bei der sich in der Gate-Polysiliziumschicht neben dem Gate-Dielektrikum eine Verarmungsschicht bildet, wenn sich der Transistor in der Inversion befindet. Um dieses Problem zu vermeiden, wird ein Metall-Gate gewünscht. Eine Vielzahl von Metall-Gates wie Tantal, Wolfram, Tantalnitrid und Titannitrid werden verwendet, in der Regel in Verbindung mit hoch-κ-Dielektrika. Eine Alternative ist die Verwendung vollständig silizidierter Polysilizium-Gates, ein als FUSI bekanntes Verfahren. ⓘ

In den heutigen Hochleistungs-CPUs wird die Metall-Gate-Technologie in Verbindung mit hoch-κ-Dielektrika verwendet, eine Kombination, die als High-κ-Metal-Gate (HKMG) bekannt ist. Die Nachteile von Metallgattern werden durch einige Techniken überwunden:

- Die Schwellenspannung wird durch Einfügen einer dünnen "Arbeitsfunktions-Metall"-Schicht zwischen dem hoch-κ-Dielektrikum und dem Hauptmetall eingestellt. Diese Schicht ist so dünn, dass die Gesamtarbeitsfunktion des Gates sowohl durch die Arbeitsfunktion des Hauptmetalls als auch durch die des dünnen Metalls beeinflusst wird (entweder durch Legieren während des Glühens oder einfach durch die unvollständige Abschirmung durch das dünne Metall). Die Schwellenspannung kann also durch die Dicke der dünnen Metallschicht eingestellt werden.

- Hoch-κ-Dielektrika sind inzwischen gut erforscht, und ihre Defekte sind bekannt.

- Es gibt HKMG-Verfahren, bei denen die Metalle nicht bei hohen Temperaturen geglüht werden müssen; bei anderen Verfahren werden Metalle ausgewählt, die den Glühvorgang überstehen können. ⓘ

Isolator

Bei der Verkleinerung von Bauelementen werden die Isolierschichten immer dünner, oft durch thermische Oxidation oder lokale Oxidation von Silizium (LOCOS). Bei Bauelementen im Nanomaßstab kommt es irgendwann zum Tunneln von Ladungsträgern durch den Isolator vom Kanal zur Gate-Elektrode. Um den daraus resultierenden Leckstrom zu verringern, kann der Isolator dünner gemacht werden, indem ein Material mit einer höheren Dielektrizitätskonstante gewählt wird. Um zu sehen, wie Dicke und Dielektrizitätskonstante zusammenhängen, beachten Sie, dass das Gauß'sche Gesetz das Feld mit der Ladung wie folgt verknüpft:

mit Q = Ladungsdichte, κ = Dielektrizitätskonstante, ε0 = Dielektrizitätskonstante des leeren Raums und E = elektrisches Feld. Aus diesem Gesetz geht hervor, dass die gleiche Ladung im Kanal bei einem geringeren Feld aufrechterhalten werden kann, sofern κ erhöht wird. Die Spannung am Gate ist gegeben durch:

mit VG = Gate-Spannung, Vch = Spannung an der Kanalseite des Isolators und tins = Dicke des Isolators. Diese Gleichung zeigt, dass die Gate-Spannung nicht zunimmt, wenn die Dicke des Isolators zunimmt, vorausgesetzt, dass κ zunimmt, um tins / κ = konstant zu halten (siehe den Artikel über hoch-κ-Dielektrika für weitere Einzelheiten und den Abschnitt in diesem Artikel über Gate-Oxid-Leckagen). ⓘ

Der Isolator in einem MOSFET ist ein Dielektrikum, das auf jeden Fall Siliziumoxid sein kann, das durch LOCOS gebildet wird, aber auch viele andere dielektrische Materialien werden verwendet. Der Oberbegriff für das Dielektrikum ist Gate-Dielektrikum, da das Dielektrikum direkt unterhalb der Gate-Elektrode und oberhalb des Kanals des MOSFETs liegt. ⓘ

Gestaltung des Anschlusses

Den Source-to-body- und Drain-to-body-Übergängen wird wegen dreier wichtiger Faktoren große Aufmerksamkeit geschenkt: Ihr Design beeinflusst die Strom-Spannungs-Kennlinie des Bauelements, wodurch der Ausgangswiderstand gesenkt wird, und auch die Geschwindigkeit des Bauelements durch den Ladeeffekt der Übergangskapazitäten und schließlich die Komponente der Stand-by-Verlustleistung aufgrund von Leckagen am Übergang. ⓘ

Die durch den Drain induzierte Absenkung der Schwellenspannung und die Auswirkungen der Kanallängenmodulation auf die I-U-Kurven werden durch die Verwendung von flachen Sperrschichtverlängerungen reduziert. Außerdem kann die Halo-Dotierung verwendet werden, d. h. das Hinzufügen sehr dünner, stark dotierter Bereiche desselben Dotierungstyps wie der Körper, die dicht an den Übergangswänden anliegen, um die Ausdehnung der Verarmungsbereiche zu begrenzen. ⓘ

Die kapazitiven Effekte werden durch die Verwendung erhöhter Source- und Drain-Geometrien begrenzt, bei denen der größte Teil der Kontaktfläche aus einem dicken Dielektrikum anstelle von Silizium besteht. ⓘ

Diese verschiedenen Merkmale des Übergangsdesigns sind (mit künstlerischer Freiheit) in der Abbildung dargestellt. ⓘ

Skalierung

In den letzten Jahrzehnten wurde der MOSFET (wie er für die digitale Logik verwendet wird) kontinuierlich verkleinert; typische MOSFET-Kanallängen betrugen früher mehrere Mikrometer, aber moderne integrierte Schaltungen enthalten MOSFETs mit Kanallängen von einigen zehn Nanometern. Robert Dennards Arbeit an der Skalierungstheorie war ausschlaggebend für die Erkenntnis, dass diese kontinuierliche Verkleinerung möglich war. Intel begann Ende 2009 mit der Produktion eines Prozesses mit einer Strukturgröße von 32 nm (wobei der Kanal noch kürzer ist). Die Halbleiterindustrie unterhält eine "Roadmap", die ITRS, die das Tempo für die MOSFET-Entwicklung vorgibt. In der Vergangenheit waren die Schwierigkeiten bei der Verkleinerung von MOSFETs mit dem Herstellungsprozess von Halbleiterbauelementen, der Notwendigkeit, sehr niedrige Spannungen zu verwenden, und mit einer schlechteren elektrischen Leistung verbunden, die eine Neugestaltung und Innovation der Schaltungen erforderte (kleine MOSFETs weisen höhere Leckströme und einen geringeren Ausgangswiderstand auf). ⓘ

Kleinere MOSFETs sind aus mehreren Gründen wünschenswert. Der Hauptgrund für die Verkleinerung der Transistoren besteht darin, immer mehr Bauelemente auf einer bestimmten Chipfläche unterzubringen. Dies führt zu einem Chip mit der gleichen Funktionalität auf kleinerer Fläche oder zu Chips mit mehr Funktionalität auf gleicher Fläche. Da die Herstellungskosten für einen Halbleiterwafer relativ fest sind, hängen die Kosten pro integrierten Schaltkreis hauptsächlich von der Anzahl der Chips ab, die pro Wafer produziert werden können. Kleinere ICs ermöglichen daher mehr Chips pro Wafer, wodurch der Preis pro Chip sinkt. In den letzten 30 Jahren hat sich die Anzahl der Transistoren pro Chip alle 2-3 Jahre verdoppelt, sobald ein neuer Technologieknoten eingeführt wurde. So kann beispielsweise die Anzahl der MOSFETs in einem Mikroprozessor, der in einer 45-nm-Technologie hergestellt wird, durchaus doppelt so hoch sein wie in einem 65-nm-Chip. Diese Verdoppelung der Transistordichte wurde erstmals 1965 von Gordon Moore beobachtet und wird gemeinhin als Moore'sches Gesetz bezeichnet. Es wird auch erwartet, dass kleinere Transistoren schneller schalten. Ein Ansatz zur Größenreduzierung ist beispielsweise eine Skalierung des MOSFET, bei der sich alle Abmessungen des Bauelements proportional verringern müssen. Die wichtigsten Abmessungen des Bauelements sind die Kanallänge, die Kanalbreite und die Oxiddicke. Wenn sie um den gleichen Faktor verkleinert werden, ändert sich der Kanalwiderstand des Transistors nicht, während die Gate-Kapazität um diesen Faktor verringert wird. Daher skaliert die RC-Verzögerung des Transistors mit einem ähnlichen Faktor. Während dies bei den älteren Technologien traditionell der Fall war, führt eine Verkleinerung der Transistorabmessungen bei den modernen MOSFETs nicht unbedingt zu einer höheren Chip-Geschwindigkeit, da die Verzögerung durch die Verbindungsleitungen stärker ins Gewicht fällt. ⓘ

Die Herstellung von MOSFETs mit Kanallängen von weniger als einem Mikrometer ist eine Herausforderung, und die Schwierigkeiten bei der Herstellung von Halbleiterbauelementen sind immer ein limitierender Faktor bei der Weiterentwicklung der integrierten Schaltungstechnologie. Obwohl Verfahren wie ALD die Herstellung von kleinen Bauteilen verbessert haben, hat die geringe Größe der MOSFETs (weniger als einige zehn Nanometer) zu betrieblichen Problemen geführt:

- Höhere Unterschwellenleitfähigkeit

- Da die MOSFET-Geometrien immer kleiner werden, muss die Spannung, die an das Gate angelegt werden kann, reduziert werden, um die Zuverlässigkeit zu erhalten. Um die Leistung aufrechtzuerhalten, muss auch die Schwellenspannung des MOSFETs reduziert werden. Wenn die Schwellenspannung verringert wird, kann der Transistor mit dem begrenzten Spannungshub nicht mehr vom vollständigen Ausschalten zum vollständigen Einschalten umgeschaltet werden; das Schaltungsdesign ist ein Kompromiss zwischen starkem Strom im Ein-Zustand und geringem Strom im Aus-Zustand, und die Anwendung bestimmt, ob das eine dem anderen vorgezogen wird. Subthreshold-Leckage (einschließlich Subthreshold-Leitung, Gate-Oxid-Leckage und Sperrschicht-Leckage), die in der Vergangenheit vernachlässigt wurde, kann heute mehr als die Hälfte des Gesamtstromverbrauchs moderner Hochleistungs-VLSI-Chips verbrauchen.

- Erhöhte Gate-Oxid-Leckage

- Das Gate-Oxid, das als Isolator zwischen Gate und Kanal dient, sollte so dünn wie möglich sein, um die Leitfähigkeit des Kanals und die Leistung zu erhöhen, wenn der Transistor eingeschaltet ist, und um die Leckage unter der Schwelle zu verringern, wenn der Transistor ausgeschaltet ist. Bei den derzeitigen Gate-Oxiden mit einer Dicke von etwa 1,2 nm (was bei Silizium einer Dicke von ~5 Atomen entspricht) tritt jedoch das quantenmechanische Phänomen des Elektronentunnelns zwischen Gate und Kanal auf, was zu einem erhöhten Stromverbrauch führt. Siliziumdioxid wird traditionell als Gate-Isolator verwendet. Siliziumdioxid hat jedoch eine bescheidene Dielektrizitätskonstante. Eine Erhöhung der Dielektrizitätskonstante des Gate-Dielektrikums ermöglicht eine dickere Schicht bei gleichbleibend hoher Kapazität (die Kapazität ist proportional zur Dielektrizitätskonstante und umgekehrt proportional zur Dielektrikumsdicke). Unter sonst gleichen Bedingungen verringert eine größere dielektrische Dicke den Quantentunnelstrom durch das Dielektrikum zwischen Gate und Kanal. Isolatoren, die eine größere Dielektrizitätskonstante als Siliziumdioxid aufweisen (so genannte Hoch-κ-Dielektrika), wie Metallsilikate der Gruppe IVb, z. B. Hafnium- und Zirkoniumsilikate und -oxide, werden ab dem 45-Nanometer-Technologieknoten zur Verringerung des Gate-Leckstroms eingesetzt. Andererseits ist die Barrierenhöhe des neuen Gate-Isolators ein wichtiger Faktor; der Unterschied in der Leitungsbandenergie zwischen dem Halbleiter und dem Dielektrikum (und der entsprechende Unterschied in der Valenzbandenergie) wirkt sich ebenfalls auf die Höhe des Leckstroms aus. Für das traditionelle Gate-Oxid, Siliziumdioxid, liegt die ehemalige Barriere bei etwa 8 eV. Bei vielen alternativen Dielektrika ist der Wert deutlich niedriger, was den Tunnelstrom tendenziell erhöht und den Vorteil der höheren Dielektrizitätskonstante etwas zunichte macht. Die maximale Gate-Source-Spannung wird durch die Stärke des elektrischen Feldes bestimmt, das das Gate-Dielektrikum aushalten kann, bevor es zu einem signifikanten Leckstrom kommt. Je dünner das isolierende Dielektrikum ist, desto höher ist die elektrische Feldstärke bei einer festen Spannung. Dies macht es erforderlich, mit dem dünneren Dielektrikum niedrigere Spannungen zu verwenden.

- Erhöhte Sperrschichtleckage

- Um die Bauelemente zu verkleinern, ist das Design der Übergänge komplexer geworden, was zu höheren Dotierungsniveaus, flacheren Übergängen, "Halo"-Dotierung usw. führt, um die durch das Drain verursachte Absenkung der Barriere zu verringern (siehe den Abschnitt über das Design der Übergänge). Um diese komplexen Übergänge zu erhalten, müssen die früher zur Beseitigung von Schäden und elektrisch aktiven Defekten angewandten Glühschritte eingeschränkt werden, wodurch sich die Leckage an den Übergängen erhöht. Eine stärkere Dotierung geht auch mit dünneren Verarmungsschichten und mehr Rekombinationszentren einher, die zu einem erhöhten Leckstrom führen, auch ohne Gitterschäden.

- Drain-induzierte Barrierenabsenkung (DIBL) und VT-Rolloff

- Aufgrund des Kurzkanaleffekts erfolgt die Kanalbildung nicht mehr ausschließlich durch das Gate, sondern auch Drain und Source beeinflussen die Kanalbildung. Mit abnehmender Kanallänge nähern sich die Verarmungsbereiche von Source und Drain an und machen die Schwellenspannung (VT) zu einer Funktion der Kanallänge. Dies wird als VT-Roll-off bezeichnet. VT ist auch eine Funktion der Drain-Source-Spannung VDS. Wenn wir die VDS erhöhen, werden die Verarmungsgebiete größer, und eine beträchtliche Menge an Ladung wird durch die VDS verbraucht. Die zur Bildung des Kanals erforderliche Gate-Spannung wird dann gesenkt, und somit sinkt die VT mit einer Erhöhung der VDS. Dieser Effekt wird als "drain induced barrier lowering" (DIBL) bezeichnet.

- Niedrigerer Ausgangswiderstand

- Für den Analogbetrieb ist für eine gute Verstärkung eine hohe MOSFET-Ausgangsimpedanz erforderlich, d. h. der MOSFET-Strom sollte nur geringfügig von der angelegten Drain-Source-Spannung abhängen. Da die Bauelemente immer kleiner werden, konkurriert der Einfluss des Drains immer stärker mit dem des Gates, da diese beiden Elektroden immer näher beieinander liegen, was die Empfindlichkeit des MOSFET-Stroms gegenüber der Drain-Spannung erhöht. Um der daraus resultierenden Verringerung des Ausgangswiderstands entgegenzuwirken, werden die Schaltungen komplexer, indem entweder mehr Bauelemente benötigt werden, z. B. Kaskoden- und Kaskadenverstärker, oder indem Rückkopplungsschaltungen mit Operationsverstärkern eingesetzt werden, z. B. eine Schaltung wie die in der nebenstehenden Abbildung.

- Niedrigere Transkonduktanz

- Die Transkonduktanz des MOSFET bestimmt seine Verstärkung und ist proportional zur Loch- oder Elektronenbeweglichkeit (je nach Bauelementetyp), zumindest bei niedrigen Drain-Spannungen. Wenn die MOSFET-Größe verringert wird, nehmen die Felder im Kanal zu und die Dotierstoff-Verunreinigungsgrade steigen. Beide Veränderungen verringern die Ladungsträgerbeweglichkeit und damit die Transkonduktanz. Wenn die Kanallänge ohne proportionale Verringerung der Drain-Spannung verringert wird und das elektrische Feld im Kanal ansteigt, führt dies zu einer Sättigung der Ladungsträger, wodurch der Strom und die Transkonduktanz begrenzt werden.

- Verbindungskapazität

- Traditionell war die Schaltzeit ungefähr proportional zur Gate-Kapazität der Gates. Da die Transistoren jedoch immer kleiner werden und immer mehr Transistoren auf dem Chip platziert werden, macht die Verbindungskapazität (die Kapazität der Metallschichtverbindungen zwischen verschiedenen Teilen des Chips) einen großen Teil der Kapazität aus. Die Signale müssen durch die Zwischenverbindungen geleitet werden, was zu einer größeren Verzögerung und geringeren Leistung führt.

- Wärmeentwicklung

- Die ständig zunehmende Dichte von MOSFETs auf einem integrierten Schaltkreis führt zu Problemen mit einer erheblichen lokalen Wärmeentwicklung, die den Betrieb des Schaltkreises beeinträchtigen kann. Die Schaltkreise arbeiten bei hohen Temperaturen langsamer, sind weniger zuverlässig und haben eine kürzere Lebensdauer. Kühlkörper und andere Kühlvorrichtungen und -methoden sind jetzt für viele integrierte Schaltungen, einschließlich Mikroprozessoren, erforderlich. Bei Leistungs-MOSFETs besteht die Gefahr des thermischen Durchgehens. Da ihr Durchlasswiderstand mit der Temperatur ansteigt, steigt bei einer Last mit annähernd konstantem Strom die Verlustleistung entsprechend an und erzeugt weitere Wärme. Wenn der Kühlkörper nicht in der Lage ist, die Temperatur niedrig genug zu halten, kann die Sperrschichttemperatur schnell und unkontrolliert ansteigen, was zur Zerstörung des Bauteils führt.

- Prozessvariationen

- Da MOSFETs immer kleiner werden, verringert sich die Anzahl der Atome im Silizium, die viele Eigenschaften des Transistors bewirken, so dass die Kontrolle über die Anzahl der Dotierstoffe und deren Platzierung unregelmäßiger ist. Bei der Chipherstellung wirken sich zufällige Prozessschwankungen auf alle Transistordimensionen aus: Länge, Breite, Übergangstiefen, Oxiddicke usw., und ihr Anteil an der Gesamtgröße des Transistors wird mit zunehmender Schrumpfung des Transistors größer. Die Transistoreigenschaften werden unsicherer, mehr statistisch. Der Zufallscharakter der Herstellung bedeutet, dass wir nicht wissen, welche MOSFETs in einer bestimmten Schaltung zum Einsatz kommen werden. Diese Ungewissheit zwingt zu einem weniger optimalen Entwurf, da der Entwurf für eine große Vielfalt möglicher Komponenten-MOSFETs funktionieren muss. Siehe Prozessvariation, Design for Manufacturability, Zuverlässigkeitstechnik und statistische Prozesskontrolle.

- Herausforderungen bei der Modellierung

- Moderne ICs werden am Computer simuliert, mit dem Ziel, funktionierende Schaltungen aus dem ersten Fertigungslos zu erhalten. Durch die Miniaturisierung der Bauelemente ist es aufgrund der Komplexität der Verarbeitung schwierig, genau vorherzusagen, wie die endgültigen Bauelemente aussehen werden, und auch die Modellierung der physikalischen Prozesse wird immer schwieriger. Darüber hinaus erfordern mikroskopische Variationen in der Struktur, die einfach auf die Wahrscheinlichkeit atomarer Prozesse zurückzuführen sind, statistische (und nicht nur deterministische) Vorhersagen. Diese Faktoren zusammengenommen erschweren eine angemessene Simulation und eine "gleich beim ersten Mal" richtige Herstellung. ⓘ

Andere Typen

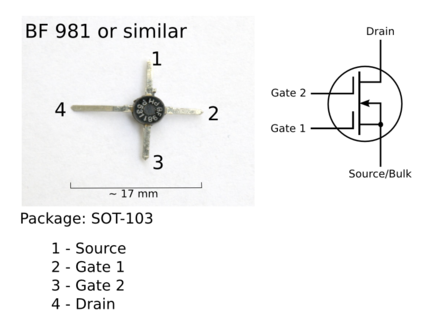

Dual-Gate

Der Dual-Gate-MOSFET hat eine Tetroden-Konfiguration, bei der beide Gates den Strom im Bauelement steuern. Er wird häufig für Kleinsignalbauelemente in Hochfrequenzanwendungen verwendet, bei denen die Vorspannung des drain-seitigen Gates auf konstantem Potenzial den durch den Miller-Effekt verursachten Verstärkungsverlust verringert und zwei separate Transistoren in Kaskodenkonfiguration ersetzt. Weitere gängige Anwendungen in HF-Schaltungen sind Verstärkungsregelung und Mischen (Frequenzumwandlung). Die Beschreibung der Tetrode ist zwar zutreffend, gibt aber nicht die Vakuumröhren-Tetrode wieder. Vakuumröhren-Tetroden, die ein Schirmgitter verwenden, weisen eine viel geringere Gitterplattenkapazität und eine viel höhere Ausgangsimpedanz und Spannungsverstärkung auf als Trioden-Vakuumröhren. Diese Verbesserungen betragen in der Regel eine Größenordnung (10-fach) oder deutlich mehr. Tetroden-Transistoren (mit bipolarem Übergang oder Feldeffekt) weisen keine so großen Verbesserungen auf. ⓘ

Der FinFET ist ein Silizium-auf-Isolator-Bauelement mit doppeltem Gate, eine von mehreren Geometrien, die eingeführt wurden, um die Auswirkungen kurzer Kanäle abzuschwächen und die durch den Drain verursachte Absenkung der Barriere zu verringern. Die Finne bezieht sich auf den schmalen Kanal zwischen Source und Drain. Eine dünne isolierende Oxidschicht auf beiden Seiten der Finne trennt diese vom Gate. SOI-FinFETs mit einer dicken Oxidschicht auf der Finne werden als Double-Gate-FinFETs und solche mit einer dünnen Oxidschicht sowohl auf der Finne als auch auf den Seiten als Triple-Gate-FinFETs bezeichnet. ⓘ

FinFETs sind eine Gruppe von nicht-planaren MOSFETs, bei denen sich der leitfähige Kanal an einem dünnen Silicium-Grat (engl. fin) befindet. Die Bezeichnung wurde erstmals 1999 in einer Veröffentlichung von Forschern der University of California, Berkeley verwendet und basiert auf dem Einzelgatetransistordesign DELTA. Da sich der Kanal prinzipiell an allen Seiten des Grats befinden kann, werden oft auch Multigate-Feldeffekttransistoren wie der Dual- (Tetrode) oder Tri-Gate-MOSFET als FinFET bezeichnet. ⓘ

FinFETs bieten die Vorteile eines vergrößerten Kanalbereichs und besserer elektrischer Eigenschaften (z. B. kurze Schaltzeiten oder kleinere Leckströme). Zudem benötigen sie bei gleicher Leistungsfähigkeit weniger Platz, was eine höhere Integrationsdichte erlaubt. Eingesetzt werden sie zum Beispiel in HF-Schaltungen (HF-Verstärker, multiplikativer Mischer). Aber auch für Standardlogikschaltungen, wie Hauptprozessoren oder Mikrocontroller, werden diese alternativen Transistorvarianten zunehmend interessant. Intel setzt seit 2012 mit der 22-nm-Technologie Ivy Bridge erstmals FinFETs in der Massenproduktion für Prozessoren ein. Seit 2014 bietet auch TSMC einen 16-nm-FinFET-Prozess für die Halbleiterindustrie an; ab 2022 plant das Unternehmen die 3-nm-Volumenfertigung. ⓘ

Darstellung eines Dual-Gate-MOSFET BF981 (oder ähnlicher Typ). Im Schaltsymbol wurden die Schutzdioden an den Gates weggelassen. ⓘ

Verarmungsmodus

Es gibt MOSFETs im Verarmungsmodus, die weniger häufig verwendet werden als die bereits beschriebenen Standard-MOSFETs im Anreicherungsmodus. Dabei handelt es sich um MOSFET-Bauelemente, die so dotiert sind, dass auch bei Nullspannung zwischen Gate und Source ein Kanal vorhanden ist. Um den Kanal zu steuern, wird eine negative Spannung an das Gate (bei einem n-Kanal-Bauelement) angelegt, wodurch der Kanal verarmt und der Stromfluss durch das Bauelement verringert wird. Im Wesentlichen entspricht das Bauelement im Verarmungsmodus einem normalerweise geschlossenen (ein) Schalter, während das Bauelement im Anreicherungsmodus einem normalerweise offenen (aus) Schalter entspricht. ⓘ

Aufgrund ihrer niedrigen Rauschzahl im HF-Bereich und ihrer besseren Verstärkung werden diese Bauelemente in HF-Frontends, z. B. in Fernsehgeräten, häufig gegenüber Bipolaren bevorzugt. ⓘ

Zu den MOSFET-Familien im Verarmungsmodus gehören der BF960 von Siemens und Telefunken sowie der BF980 von Philips (später NXP Semiconductors), dessen Derivate immer noch in AGC- und HF-Mischer-Frontends verwendet werden. ⓘ

Metall-Isolator-Halbleiter-Feldeffekttransistor (MISFET)

Metall-Isolator-Halbleiter-Feldeffekttransistor oder MISFET ist ein allgemeinerer Begriff als MOSFET und ein Synonym für Isolierschicht-Feldeffekttransistor (IGFET). Alle MOSFETs sind MISFETs, aber nicht alle MISFETs sind MOSFETs. ⓘ

Das Gate-Dielektrikum in einem MISFET ist bei einem MOSFET Siliziumdioxid, es können aber auch andere Materialien verwendet werden. Das Gate-Dielektrikum liegt direkt unterhalb der Gate-Elektrode und oberhalb des Kanals des MISFETs. In der Vergangenheit wurde für das Gate-Material der Begriff Metall verwendet, auch wenn es sich heute in der Regel um hochdotiertes Polysilizium oder ein anderes Nichtmetall handelt. ⓘ

Als Isolator können verwendet werden:

- Siliziumdioxid, in MOSFETs

- Organische Isolatoren (z. B. undotiertes Trans-Polyacetylen; Cyanoethyl-Pullulan, CEP) für FETs auf organischer Basis. ⓘ

NMOS-Logik

Bei gleicher Strombelastbarkeit können n-Kanal-MOSFETs kleiner gebaut werden als p-Kanal-MOSFETs, da die Mobilität der p-Kanal-Ladungsträger (Löcher) geringer ist als die der n-Kanal-Ladungsträger (Elektronen) und die Herstellung von nur einem MOSFET-Typ auf einem Siliziumsubstrat billiger und technisch einfacher ist. Dies waren die treibenden Prinzipien bei der Entwicklung der NMOS-Logik, die ausschließlich n-Kanal-MOSFETs verwendet. Im Gegensatz zur CMOS-Logik verbraucht die NMOS-Logik jedoch auch dann Strom, wenn keine Schaltvorgänge stattfinden, wenn man den Leckstrom vernachlässigt. Mit den technologischen Fortschritten verdrängte die CMOS-Logik Mitte der 1980er Jahre die NMOS-Logik und wurde zum bevorzugten Verfahren für digitale Chips. ⓘ

Leistungs-MOSFET

Leistungs-MOSFETs haben eine andere Struktur. Wie bei den meisten Leistungsbauelementen ist die Struktur vertikal und nicht planar. Durch die vertikale Struktur ist es dem Transistor möglich, sowohl eine hohe Sperrspannung als auch einen hohen Strom zu liefern. Die Nennspannung des Transistors ist eine Funktion der Dotierung und der Dicke der N-epitaktischen Schicht (siehe Querschnitt), während die Stromstärke eine Funktion der Kanalbreite ist (je breiter der Kanal, desto höher der Strom). Bei einer planaren Struktur sind sowohl die Stromstärke als auch die Durchbruchsspannung eine Funktion der Kanalabmessungen (Breite bzw. Länge des Kanals), was zu einer ineffizienten Nutzung der "Siliziumfläche" führt. Bei der vertikalen Struktur ist die Bauteilfläche ungefähr proportional zum Strom, den sie aufnehmen kann, und die Bauteildicke (eigentlich die Dicke der N-Epitaxieschicht) ist proportional zur Durchbruchspannung. ⓘ

Leistungs-MOSFETs mit lateraler Struktur werden hauptsächlich in High-End-Audioverstärkern und Hochleistungs-PA-Systemen eingesetzt. Ihr Vorteil ist ein besseres Verhalten im gesättigten Bereich (der dem linearen Bereich eines bipolaren Transistors entspricht) als bei den vertikalen MOSFETs. Vertikale MOSFETs sind für Schaltanwendungen konzipiert. ⓘ

Mit den steigenden Anforderungen an die elektrischen Eigenschaften von MOSFETs und der Notwendigkeit, mit den Effekten der Miniaturisierung bei den Transistoren (z. B. Kurzkanaleffekte) umzugehen, wurden in den vergangenen Jahrzehnten Varianten des planaren MOSFET entwickelt. Sie unterscheiden sich häufig in der Gestaltung des Dotierungsprofils oder der Materialwahl. Beispiele sind LDD-MOSFETs (von engl. lightly doped drain), Transistoren mit Halo-Implantaten oder gestrecktem Silizium sowie HKMG-Transistoren. Da in der Regel verschiedene Verbesserungen gleichzeitig genutzt werden, lässt sich hier jedoch keine Klassifikation anwenden. ⓘ

Darüber hinaus ist zwischen lateralen (also parallel zu der Oberfläche ausgerichteten) und vertikalen Bauformen zu unterscheiden. Während laterale Transistoren vorwiegend in der Nachrichtentechnik zum Einsatz kommen (lateral double-diffused MOSFET, LDMOS), findet sich die vertikale Bauform überwiegend in der Leistungselektronik wieder. Der Vorteil der vertikalen Struktur liegt in der höheren möglichen Sperrspannung der Bauelemente. ⓘ

Doppeldiffundierte Metall-Oxid-Halbleiter (DMOS)

Es gibt LDMOS (laterale doppelt-diffundierte Metalloxid-Halbleiter) und VDMOS (vertikale doppelt-diffundierte Metalloxid-Halbleiter). Die meisten Leistungs-MOSFETs werden mit dieser Technologie hergestellt. ⓘ

Strahlungsgehärtet durch Design (RHBD)

Elektronische Halbleiterschaltungen im Submikrometer- und Nanometerbereich sind das Hauptanliegen für den Betrieb innerhalb der normalen Toleranzen in rauen Strahlungsumgebungen wie dem Weltraum. Einer der Entwurfsansätze für die Herstellung eines strahlengeschützten Bauelements (RHBD) ist der ELT (enclosed-layout-transistor). Normalerweise umgibt das Gate des MOSFETs den Drain, der sich in der Mitte des ELTs befindet. Die Source des MOSFETs umgibt das Gate. Ein weiterer RHBD-MOSFET wird als H-Gate bezeichnet. Beide Transistoren haben einen sehr geringen Leckstrom in Bezug auf die Strahlung. Sie sind jedoch sehr groß und benötigen mehr Platz auf dem Silizium als ein Standard-MOSFET. Bei älteren STI-Designs (shallow trench isolation) verursachen Strahlungseinschläge in der Nähe des Siliziumoxidbereichs die Kanalinversion an den Ecken des Standard-MOSFETs aufgrund der Akkumulation von strahlungsinduzierten eingefangenen Ladungen. Wenn die Ladungen groß genug sind, wirken sich die akkumulierten Ladungen auf die STI-Oberflächenkanten entlang des Kanals in der Nähe der Kanalschnittstelle (Gate) des Standard-MOSFETs aus. Auf diese Weise kommt es zu einer Kanalinversion entlang der Kanalkanten und der Baustein erzeugt einen Leckagepfad im Aus-Zustand, der das Einschalten des Bausteins bewirkt. Die Zuverlässigkeit der Schaltungen wird dadurch stark beeinträchtigt. Der ELT bietet viele Vorteile. Zu diesen Vorteilen gehört die Verbesserung der Zuverlässigkeit durch Verringerung der unerwünschten Oberflächeninversion an den Gate-Kanten, die bei Standard-MOSFETs auftritt. Da die Gate-Kanten in ELT eingeschlossen sind, gibt es keine Gate-Oxid-Kante (STI an der Gate-Schnittstelle), so dass die Transistor-Leckage im Aus-Zustand sehr stark reduziert wird. Mikroelektronische Schaltungen mit geringem Stromverbrauch, einschließlich Computern, Kommunikationsgeräten und Überwachungssystemen in Raumfähren und Satelliten, unterscheiden sich stark von denen auf der Erde. Es handelt sich um strahlungstolerante Schaltungen (Hochgeschwindigkeits-Atomteilchen wie Protonen und Neutronen, magnetische Energieverluste durch Sonneneruptionen im Weltraum, energetische kosmische Strahlung wie Röntgen- und Gammastrahlen usw.). Diese spezielle Elektronik wird mit Hilfe verschiedener Techniken unter Verwendung von RHBD-MOSFETs entwickelt, um sichere Weltraumreisen und sichere Weltraumspaziergänge der Astronauten zu gewährleisten. ⓘ

Aufbau und Funktionsweise

Ein MOSFET ist ein aktives Bauelement mit mindestens drei Anschlüssen (Elektroden): G (gate, dt. Steuerelektrode), D (drain, dt. Abfluss), S (source, dt. Quelle). Bei einigen Bauformen wird ein zusätzlicher Anschluss B (bulk, Substrat) nach außen geführt, der mit der Chiprückseite verbunden ist. Da eine Spannung an der Chiprückseite zusätzliche elektrische Felder erzeugt, die auf den Kanal wirken, verschiebt sich, wenn man die Spannung am B-Anschluss ändert, die Threshold-Spannung des MOSFETs. Meistens ist das Substrat jedoch intern mit dem Source verbunden. ⓘ

Wie andere Feldeffekttransistoren wirkt der MOSFET wie ein spannungsgesteuerter Widerstand, das heißt, über die Gate-Source-Spannung UGS kann der Widerstand zwischen Drain und Source RDS und somit der Strom IDS (vereinfacht ID) durch RDS um mehrere Größenordnungen geändert werden. Der Schlüssel zum Verständnis dieser Widerstandsänderung in einer MOS-Struktur liegt in der Entstehung (Anreicherungstypen) bzw. Abschnürung (Verarmungstypen) eines leitenden Kanals unter dem Gate (Details siehe unten). ⓘ

Zuordnung der Source- und Drain-Gebiete bei PMOS und NMOS

Source bezeichnet den Anschluss, von dem die für den Ladungstransport verantwortlichen Ladungsträger (Majoritätsladungsträger) im leitenden Fall in Richtung des Drain-Anschlusses driften. ⓘ

Beim p-Kanal-MOSFET (PMOS, PMOSFET) bilden Defektelektronen (Löcher) die Majoritätsladungsträger, sie fließen in Richtung der technischen Stromrichtung. Bei der Beschaltung von p-Kanal-MOSFET ist das Source-Potential (+, näher an gelegen) größer als das Drain-Potential (−; näher an gelegen). ⓘ

Beim n-Kanal-MOSFET (NMOS, NMOSFET) bilden hingegen Elektronen die Majoritätsladungsträger. Sie fließen entgegen der technischen Stromrichtung. Bezüglich des elektrischen Potentials ist daher die Lage von Source und Drain entgegengesetzt zum p-Kanal-MOSFET. Das heißt, das Source-Potential (−; näher an gelegen) ist geringer als das Drain-Potential (+; näher an gelegen). ⓘ

Kennlinienfeld

| Symbol | Berechnung | Beschreibung |

|---|---|---|

| Ausgangsspannung zwischen Drain und Source | ||

| Eingangsspannung zwischen Gate und Source | ||

| Spannung zwischen Source und Back-Gate, auch Bulk-Anschluss genannt | ||

| positive Versorgungsspannung aus NMOS, wird auch in CMOS-Technik verwendet | ||

| negative Versorgungsspannung aus NMOS, wird auch in CMOS-Technik verwendet |

Schwellenspannung

Die Schwellenspannung (engl.: threshold voltage) stellt ein zentrales Element bei der Modellbetrachtung von MOSFETs dar und hängt stark von der Prozesstechnik ab. Dabei entscheiden die Dotierungen von Source, Drain und des Kanalgebietes über die Größe der Schwellenspannung. ⓘ

- für NMOS-Verarmungstyp und PMOS-Anreicherungstyp

- für NMOS-Anreicherungstyp und PMOS-Verarmungstyp, typ. zwischen 1 V und 3 V. ⓘ

Zudem ist die Schwellenspannung abhängig von der Temperatur. Für die Beschreibung reicht die Abhängigkeit 1. Ordnung (lineare Abhängigkeit):

wobei der Temperaturkoeffizient, die Temperatur und die Stütztemperatur (beispielsweise die typische Betriebstemperatur) ist. ⓘ

Ausgangskennlinienfeld

Die Darstellung der Zusammenhänge zwischen dem Drain-Strom (auch , Drain-Source-Strom) und der Drain-Source-Spannung in Abhängigkeit von der Gate-Source-Spannung wird als Ausgangskennlinienfeld eines MOSFETs bezeichnet. Es ist für alle MOSFETs (NMOS-Anreicherungstyp, NMOS-Verarmungstyp, PMOS-Anreicherungstyp und PMOS-Verarmungstyp) prinzipiell gleich. Unterschiede ergeben sich nur in den Potentialbezugspunkten von Drain und Source, sowie im Vorzeichen des Verstärkungsfaktors. Die Kennlinien werden durch weitere Effekte (Temperatur, Substratvorspannung, Kurzkanaleffekte etc.) beeinflusst. ⓘ

Die einzelne ID-UDS-Kennlinie eines MOSFETs unterteilt sich in drei Bereiche: den Sperrbereich, den aktiven Bereich und den Sättigungsbereich. ⓘ

Sperrbereich

Im Sperrbereich (engl. cutoff region), auch Abschaltbereich oder Unterschwellenbereich (engl. subthreshold region) genannt, liegt die Gate-Source-Spannung unterhalb der Schwellenspannung . ⓘ

Für gilt:

mit

- dem Schwellenspannungsstrom (engl.: threshold current)

- dem subthreshold swing (Kehrwert von subthreshold slope, Unterschwellensteilheit)

- der Temperaturspannung ,

- der Boltzmannkonstante ,

- die Ladung der beteiligten Ladungsträger (≙ Elementarladung),

- dem Emissionsfaktor im Unterschwellenbereich (engl. sub-threshold slope factor) und

- der Verarmungskapazität (engl.: depletion capacitance), diese setzt sich aus den Überlappkapazitäten an Drain und Source zusammen ⓘ

Der Leckstrom (engl.: leakage current) eines Anreicherungs-MOSFET berechnet sich aus der Gleichung für den Sperrbereich:

- (nur für NMOS-Anreicherungs- und PMOS-Anreicherungs-Typ). ⓘ

Linearer Bereich

Im linearen Bereich (auch Triodenbereich, ohmscher Bereich oder aktiver Bereich genannt, engl.: (triode region oder ohmic region)) liegt die Gate-Source-Spannung über der Schwellenspannung (Im Fall des Anreicherungs-MOSFET), sodass ein durchgehender Kanal zwischen Drain und Source entsteht. Der Bereich wird durch die Kennlinie der Grenzspannung begrenzt. ⓘ

Die Bezeichnung stammt von dem Umstand, dass die Kennlinien bei nahezu linear durch den Ursprung verlaufen, was dem Verhalten eines ohmschen Widerstands entspricht. ⓘ

Für und gilt:

mit

- dem NMOS-Verstärkungsfaktor (n-dotiert) ,

- dem PMOS-Verstärkungsfaktor (p-dotiert) ,

- der Ladungsträgerbeweglichkeit der Elektronen in n- bzw. p-dotiertem Substrat bzw.

- der flächenspezifische Kapazität des Gate-Kondensators

- der Weite und der Länge des Gates,

- der Dicke des Gate-Dielektrikums,

- der Permittivität des jeweiligen Materials, z. B. Silizium als Substrat und Siliziumdioxid als Dielektrikum ⓘ

Sättigungsbereich

Im Sättigungsbereich (engl. saturation region, active mode, Abschnürbereich genannt) verläuft die IDS-UDS-Kennlinie näherungsweise parallel zur -Achse. Das heißt, wird die Spannung zwischen Drain und Source erhöht, hat dies kaum einen steigernden Effekt auf den Strom, der zwischen diesen Kontakten fließt. Die Grenze, ab der sich dieses Verhalten zeigt, wird als definiert. Wie im Ausgangskennlinienfeld zu sehen, kann allerdings die Eingangsspannung genutzt werden, um den Strom direkt zu beeinflussen. In diesem Fall verhält sich der Transistor wie eine durch die Eingangsspannung gesteuerte Stromquelle. Weitere Effekte entstehen durch die Kanallängenmodulation. ⓘ

Falls die Eingangsspannung am Transistor oberhalb der Threshold-Spannung liegt:

- , ⓘ

und die Ausgangsspannung oberhalb der Sättigungsspannung (bzw. Abschnürspannung) liegt:

dann gilt für den Strom im Ausgangskreis:

Beim Vergleich mit einem Bipolartransistor muss bei der Verwendung des Begriffs Sättigungsbereich darauf geachtet werden, dass der Begriff Sättigung beim Bipolartransistor eine andere Bedeutung hat. ⓘ

Kennlinieneffekte